Go to the source code of this file.

Macros | |

| #define | EXTERN extern |

| #define | PLLSELOFF 0x7F /* Mask for switching to base external OSCCLK clock 0b_0111_1111 */ |

| #define | PLLOFF 0xBF /* Mask for turning the PLLON bit to ZERO 0b_1011_1111, IE, turning PLL off */ |

| #define | PLLDIVISOR 0x03 /* Input crystal frequency is divided by this number */ |

| #define | PLLMULTIPLIER 0x09 /* The result of the above is multiplied by this number to give the bus frequency */ |

| #define | PRDIV8 0x40 /* Mask for flash module to divide the oscillator clock by 8 */ |

Functions | |

| void | init (void) FPAGE_FE |

| The main top level init. | |

| void | enablePLL (void) FPAGE_FE |

| Switch to using PLL. | |

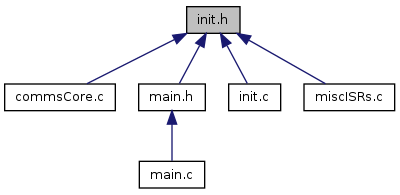

Detailed Description

Definition in file init.h.

Macro Definition Documentation

| #define PLLSELOFF 0x7F /* Mask for switching to base external OSCCLK clock 0b_0111_1111 */ |

| #define PLLOFF 0xBF /* Mask for turning the PLLON bit to ZERO 0b_1011_1111, IE, turning PLL off */ |

| #define PLLDIVISOR 0x03 /* Input crystal frequency is divided by this number */ |

| #define PLLMULTIPLIER 0x09 /* The result of the above is multiplied by this number to give the bus frequency */ |

| #define PRDIV8 0x40 /* Mask for flash module to divide the oscillator clock by 8 */ |

Function Documentation

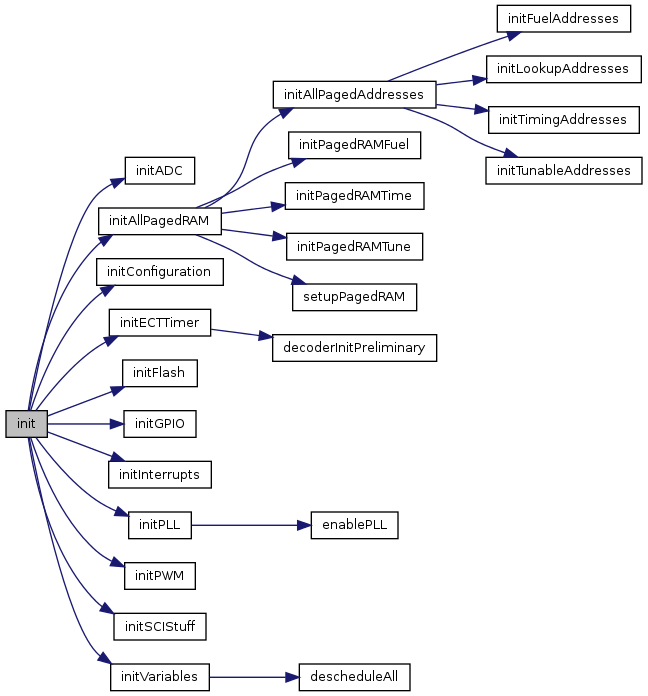

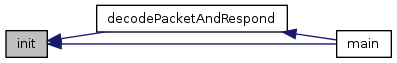

| void init | ( | void | ) |

The main top level init.

The main init function to be called from main.c before entering the main loop. This function is simply a delegator to the finer grained special purpose init functions.

Definition at line 61 of file init.c.

References ATOMIC_END, ATOMIC_START, initADC(), initAllPagedRAM(), initConfiguration(), initECTTimer(), initFlash(), initGPIO(), initInterrupts(), initPLL(), initPWM(), initSCIStuff(), and initVariables().

Referenced by decodePacketAndRespond(), and main().

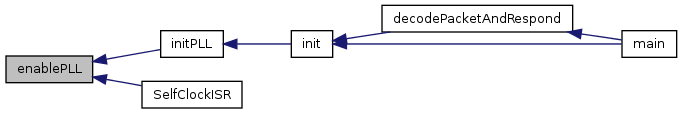

| void enablePLL | ( | void | ) |

Switch to using PLL.

Switch to using PLL for clock (40MHz bus speed). Interrupt is enabled elsewhere.

Note: Requires busy wait loop, only for init and emergency use.

- Todo:

- Should be limited, and have break out with error code and fall back mechanism.

Definition at line 108 of file init.c.

References CLKSEL, CRGFLG, PLLLOCK, and PLLSEL.

Referenced by initPLL(), and SelfClockISR().

1.8.1.2

1.8.1.2