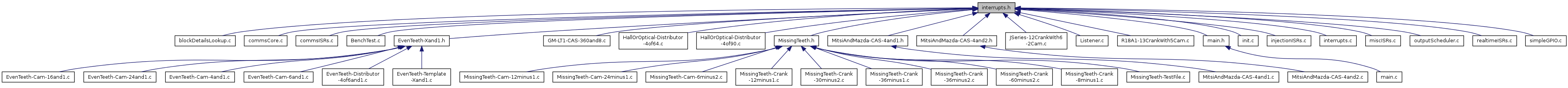

All interrupt handler declarations. More...

Go to the source code of this file.

Macros | |

| #define | INT __attribute__((interrupt)) |

| #define | ATOMIC_START() __asm__ __volatile__ ("sei") /* set global interrupt mask */ |

| #define | ATOMIC_END() __asm__ __volatile__ ("cli") /* clear global interrupt mask */ |

| #define | VECTORS __attribute__ ((section (".vectors"))) |

Typedefs | |

| typedef void(* | interruptTable )(void) |

Functions | |

| void | _start (void) |

| void | UISR (void) INT TEXT1 |

| Unimplemented Interrupt Handler. | |

| void | Injector1ISR (void) INT TEXT1 |

| This ISR is expanded from InjectorXISR via include statement, and macro definitions, so are the othe 5 below. | |

| void | Injector2ISR (void) INT TEXT1 |

| This ISR is expanded from InjectorXISR via include statement, and macro definitions, so are the othe 5 below. | |

| void | Injector3ISR (void) INT TEXT1 |

| This ISR is expanded from InjectorXISR via include statement, and macro definitions, so are the othe 5 below. | |

| void | Injector4ISR (void) INT TEXT1 |

| This ISR is expanded from InjectorXISR via include statement, and macro definitions, so are the othe 5 below. | |

| void | Injector5ISR (void) INT TEXT1 |

| This ISR is expanded from InjectorXISR via include statement, and macro definitions, so are the othe 5 below. | |

| void | Injector6ISR (void) INT TEXT1 |

| This ISR is expanded from InjectorXISR via include statement, and macro definitions, so are the othe 5 below. | |

| void | PrimaryRPMISR (void) INT TEXT1 |

| RPM ISRs, IC timer for engine position and RPM. | |

| void | SecondaryRPMISR (void) INT TEXT1 |

| RPM ISRs, IC timer for engine position and RPM. | |

| void | TimerOverflow (void) INT TEXT1 |

| ECT overflow handler. | |

| void | ModDownCtrISR (void) INT TEXT1 |

| void | IgnitionDwellISR (void) INT TEXT1 |

| void | IgnitionFireISR (void) INT TEXT1 |

| void | StagedOnISR (void) INT TEXT1 |

| void | StagedOffISR (void) INT TEXT1 |

| void | PortPISR (void) INT TEXT1 |

| Port P pins ISR. | |

| void | PortHISR (void) INT TEXT1 |

| Port H pins ISR. | |

| void | PortJISR (void) INT TEXT1 |

| Port J pins ISR. | |

| void | IRQISR (void) INT TEXT1 |

| IRQ/PE1 pin ISR. | |

| void | XIRQISR (void) INT TEXT1 |

| XIRQ/PE0 pin ISR. | |

| void | RTIISR (void) INT TEXT1 |

| Real Time Interrupt Handler. | |

| void | SCI0ISR (void) INT TEXT1 |

| Serial Communication Interface 0 ISR. | |

| void | LowVoltageISR (void) INT TEXT1 |

| Low Voltage Counter. | |

| void | VRegAPIISR (void) INT TEXT1 |

| void | PLLLockISR (void) INT TEXT1 |

| PLL Lock Lost/Gained. | |

| void | SelfClockISR (void) INT TEXT1 |

| Self Clock Mode Entered/Exited. | |

| void | SpuriousISR (void) INT TEXT1 |

| Spurious Interrupt Handler. | |

| void | UnimplOpcodeISR (void) INT TEXT1 |

| Unimplemented Opcode Handler. | |

| void | RAMViolationISR (void) INT TEXT1 |

| CPU RAM Access Violation Handler. | |

| void | XGATEErrorISR (void) INT TEXT1 |

| XGATE Software Error Handler. | |

Detailed Description

All interrupt handler declarations.

All of the declarations for ISR functions are done here because they are all used in one place and it doesn't make sense to spread them out over N files for N functions. ISR headers only exist where there is a requirement for local variables and constants etc.

Definition in file interrupts.h.

Macro Definition Documentation

| #define INT __attribute__((interrupt)) |

Definition at line 52 of file interrupts.h.

| #define ATOMIC_START | ( | ) | __asm__ __volatile__ ("sei") /* set global interrupt mask */ |

Definition at line 59 of file interrupts.h.

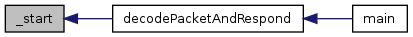

Referenced by decodePacketAndRespond(), init(), main(), performSimpleGPIO(), and scheduleOutputs().

| #define ATOMIC_END | ( | ) | __asm__ __volatile__ ("cli") /* clear global interrupt mask */ |

Definition at line 60 of file interrupts.h.

Referenced by decodePacketAndRespond(), init(), main(), performSimpleGPIO(), and scheduleOutputs().

| #define VECTORS __attribute__ ((section (".vectors"))) |

Definition at line 63 of file interrupts.h.

Typedef Documentation

| typedef void(* interruptTable)(void) |

Definition at line 124 of file interrupts.h.

Function Documentation

| void _start | ( | void | ) |

| void UISR | ( | void | ) |

Unimplemented Interrupt Handler.

Unimplemented interrupt service routine for calls we weren't expecting. Currently this simply counts bad calls like any other event type.

- Todo:

TODO Split this into its own file, create one for each, and clear flags for all, and increment shared counter as is.

TODO Currently not a problem, but as indirectly pointed out by johntramp, if no flag clearing is being done, then this code will run continuously, which is not a good idea...

Definition at line 52 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_CALLS_TO_UISRS_OFFSET, NBIT7, and PORTB.

| void Injector1ISR | ( | void | ) |

This ISR is expanded from InjectorXISR via include statement, and macro definitions, so are the othe 5 below.

- See Also

- injectorISR.c

- injectionISRs.c

| void Injector2ISR | ( | void | ) |

This ISR is expanded from InjectorXISR via include statement, and macro definitions, so are the othe 5 below.

- See Also

- injectorISR.c

- injectionISRs.c

| void Injector3ISR | ( | void | ) |

This ISR is expanded from InjectorXISR via include statement, and macro definitions, so are the othe 5 below.

- See Also

- injectorISR.c

- injectionISRs.c

| void Injector4ISR | ( | void | ) |

This ISR is expanded from InjectorXISR via include statement, and macro definitions, so are the othe 5 below.

- See Also

- injectorISR.c

- injectionISRs.c

| void Injector5ISR | ( | void | ) |

This ISR is expanded from InjectorXISR via include statement, and macro definitions, so are the othe 5 below.

- See Also

- injectorISR.c

- injectionISRs.c

| void Injector6ISR | ( | void | ) |

This ISR is expanded from InjectorXISR via include statement, and macro definitions, so are the othe 5 below.

- See Also

- injectorISR.c

- injectionISRs.c

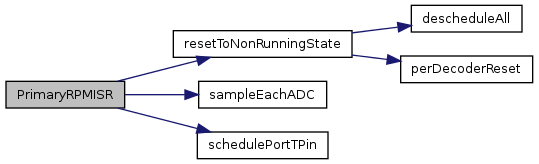

| void PrimaryRPMISR | ( | void | ) |

RPM ISRs, IC timer for engine position and RPM.

There are multiple copies of this interrupt handler, each is linked with the rest of the code once such that if there are N decoder implementations and/or variants, then there are N loadable binaries produced after a full build.

For details on any specific decoder implementation, see the documentation for that specific file.

Definition at line 85 of file BenchTest.c.

References decoderSetting::accelerationInputEventTimeTolerance, accumulatorRegisterCount, ADCBuffers, AMBIGUOUS_COUNT, ANGLE_FACTOR, angleOfSingleIteration, BackwardNarrow, BASTARD_CUMULATIVE_SYNC_LOSS_ID_BASE, BASTARD_SYNC_LOSS_ID_BASE, BIT0, CALC_FUEL_IGN, CAM_SYNC, CLEAR_BENCH_TEST_ON, Clocks, COMBUSTION_SYNC, coreStatusA, CoreVars, COUNT_OF_EVENTS_IMPOSSIBLY_HIGH_NOISE, Counters, cumulativeBastardTeeth, cumulativeBastardTeethEroderCounter, KeyUserDebug::currentEvent, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, decoderSetting::decelerationInputEventTimeTolerance, DECODER_BENCHMARKS, KeyUserDebug::decoderFlags, decoderMaxCodeTime, fixedConfig2::decoderSettings, doubleHighSeen, edgeTimeStamp, eventAngles, fixedConfigs2, FLAG_AND_INC_FLAGGABLE, FLAG_CALLS_TO_UISRS_OFFSET, KeyUserDebug::inputEventTimeTolerance, KeyUserDebugs, LAST_MATCH_VALID, LAST_PERIOD_VALID, LAST_TIMESTAMP_VALID, LAST_TPD_VALID, lastAccumulatorCount, lastEventTimeStamp, lastInterEventPeriod, twoPairs::lastPair, lastPARegisterReading, lastPrimaryEventTimeStamp, lastPrimaryTicksPerDegree, lastSecondaryEventTimeStamp, lastTicksPerDegree, MaskBySumPattern, MatchedPair, MatchedPairMatchedPair, MatchedPairNarrowWide, MAX_BASTARD_TEETH, MAX_CUMULATIVE_BASTARD_TEETH, MISSING_TEETH, decoderSetting::missingToothTolerance, NarrowBackward, NarrowWide, NarrowWideWideNarrow, NBIT0, noiseAppearedWayTooEarlyAsIfItWasAVRToothButWasnt, NUMBER_OF_REAL_EVENTS, NUMBER_OF_WHEEL_EVENTS, numberOfRealEvents, NumberOfTwinMatchedPairs, OK_TO_SCHEDULE, outputEventDelayFinalPeriod, outputEventInputEventNumbers, outputEventPulseWidthsMath, PACN1, match::pairs, match::pattern, PORTB, PRIMARY_EVENT_ARRIVED_TOO_EARLY, PRIMARY_EVENT_ARRIVED_TOO_LATE, KeyUserDebug::primaryTeethSeen, PTIT, resetToNonRunningState(), CoreVar::RPM, sampleEachADC(), schedulePortTPin(), KeyUserDebug::secondaryTeethSeen, SET_SYNC_LEVEL_TO, SHORTMAX, STATE_MISMATCH_IN_PRIMARY_RPM_ISR, Counter::syncedADCreadings, TC0, TEST_MODE_DODGY_MISSING_TOOTH, TEST_MODE_ITERATIONS, TEST_MODE_REVOLUTIONS, TEST_MODE_TIME_UNITS_HOURS, TEST_MODE_TIME_UNITS_MINUTES, TEST_MODE_TIME_UNITS_SECONDS, testEventsPerCycle, testMode, testNumberOfCycles, testNumberOfMissing, testTicksPerEvent, TFLG, TFLGOF, twoPairs::thisPair, ticks_per_degree_multiplier, ticksPerDegreeRecord, TIE, LongTime::timeLong, Clock::timeoutADCreadingClock, timerExtensionClock, LongTime::timeShorts, timeStamp, totalEventAngleRange, unknownLeadingEdges, WideNarrow, WideNarrowMatchedPair, windowCounts, windowsPerAllowedCumulativeBastardTooth, windowState, yourSyncToleranceIsLooserThanAWellYouGetTheIdea, yourSyncToleranceIsTighterThanAWellYouGetTheIdea, and yourVRSensorHasALoosePlugFixIt.

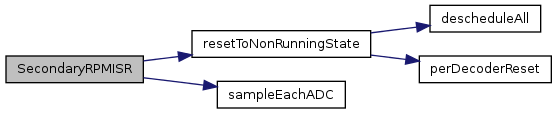

| void SecondaryRPMISR | ( | void | ) |

RPM ISRs, IC timer for engine position and RPM.

There are multiple copies of this interrupt handler, each is linked with the rest of the code once such that if there are N decoder implementations and/or variants, then there are N loadable binaries produced after a full build.For details on any specific decoder implementation, see the documentation for that specific file.

Definition at line 146 of file EvenTeeth-Xand1.c.

References decoderSetting::accelerationInputEventTimeTolerance, ADCBuffers, BIT0, BIT1, BUG_REACHED_UNREACHABLE_CODE, CALC_FUEL_IGN, CAM_SYNC, camTeethSeen, Clocks, coreStatusA, COUNT_OF_EVENTS_IMPOSSIBLY_HIGH_NOISE, COUNT_OF_EVENTS_IMPOSSIBLY_LOW_NOISE, Counters, crankTeethSinceLastCamTooth, KeyUserDebug::currentEvent, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, decoderSetting::decelerationInputEventTimeTolerance, DECODER_BENCHMARKS, KeyUserDebug::decoderFlags, fixedConfig2::decoderSettings, edgeTimeStamp, eventAngles, fixedConfigs2, FLAG_AND_INC_FLAGGABLE, FLAG_CALLS_TO_UISRS_OFFSET, KeyUserDebug::inputEventTimeTolerance, KeyUserDebugs, LAST_PERIOD_VALID, LAST_TIMESTAMP_VALID, lastEventTimeStamp, lastSecondaryEventTimeStamp, lastTicksPerDegree, NBIT0, NBIT1, NBIT2, numberOfRealEvents, OK_TO_SCHEDULE, PORTB, previousCrankTeethSeen, KeyUserDebug::primaryTeethSeen, PTIT, resetToNonRunningState(), sampleEachADC(), SECONDARY_EVENT_ARRIVED_TOO_EARLY, SECONDARY_EVENT_ARRIVED_TOO_LATE, KeyUserDebug::secondaryTeethSeen, SET_SYNC_LEVEL_TO, STATE_MISMATCH_IN_SECONDARY_RPM_ISR, Counter::syncedADCreadings, TC1, TCTL4, TFLG, TFLGOF, ticks_per_degree_multiplier, ticksPerDegreeRecord, LongTime::timeLong, Clock::timeoutADCreadingClock, timerExtensionClock, LongTime::timeShorts, and timeStamp.

| void TimerOverflow | ( | void | ) |

ECT overflow handler.

When the ECT free running timer hits 65535 and rolls over, this is run. Its job is to extend the timer to an effective 32 bits for longer measuring much longer periods with the same resolution. Please see section 10.5.5 of the 68HC11 reference manual for more information on this technique!

- Warning

- The extension var should be incremented before the flag is cleared!

Definition at line 164 of file realtimeISRs.c.

References BIT5, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, NBIT5, PORTB, TFLGOF, and timerExtensionClock.

| void ModDownCtrISR | ( | void | ) |

| void IgnitionDwellISR | ( | void | ) |

| void IgnitionFireISR | ( | void | ) |

| void StagedOnISR | ( | void | ) |

- Todo:

- TODO This will be handled by XGATE, somehow, in the mean time, move to UISR file along with others.

Definition at line 50 of file injectionISRs.c.

References PITINTE.

| void StagedOffISR | ( | void | ) |

- Todo:

- TODO This will be handled by XGATE, somehow, in the mean time, move to UISR file along with others.

Definition at line 57 of file injectionISRs.c.

References PITINTE.

| void PortPISR | ( | void | ) |

Port P pins ISR.

Interrupt handler for edge events on port P pins. Not currently used.

Definition at line 173 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_CALLS_TO_UISRS_OFFSET, NBIT7, ONES, PIFP, and PORTB.

| void PortHISR | ( | void | ) |

Port H pins ISR.

Interrupt handler for edge events on port H pins. Not currently used.

Definition at line 199 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_CALLS_TO_UISRS_OFFSET, NBIT7, ONES, PIFH, PORTB, and portHDebounce.

| void PortJISR | ( | void | ) |

Port J pins ISR.

Interrupt handler for edge events on port J pins. Not currently used.

Definition at line 186 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_CALLS_TO_UISRS_OFFSET, NBIT7, ONES, PIFJ, and PORTB.

| void IRQISR | ( | void | ) |

IRQ/PE1 pin ISR.

Interrupt handler for edge events on the IRQ/PE1 pin. Not currently used.

Definition at line 290 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_CALLS_TO_UISRS_OFFSET, NBIT7, and PORTB.

| void XIRQISR | ( | void | ) |

XIRQ/PE0 pin ISR.

Interrupt handler for edge events on the XIRQ/PE0 pin. Not currently used.

Definition at line 303 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_CALLS_TO_UISRS_OFFSET, NBIT7, and PORTB.

| void RTIISR | ( | void | ) |

Real Time Interrupt Handler.

Handles time keeping, including all internal clocks, and generic periodic tasks that run quickly and must be done on time.

- Todo:

- TODO refactor this entire file, especially to remove apparently expensive modulus operations which could be replaced with >= instead. Maybe much more.

- Todo:

- TODO This is too quick to turn off, average 0.5 seconds, which is OK, but fastest = 0seconds which is difficult to understand, needs a flag and to be 1 - 2 with average 1.5.

Definition at line 52 of file realtimeISRs.c.

References BIT3, BIT6, BIT7, CLEAR_FUEL_PUMP_PRIME, Clocks, coreStatusA, CoreVars, CRGFLG, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, fixedConfigs2, FORCE_READING, FUEL_PUMP_PRIME, sensorSetting::fuelPumpPrimePeriod, Clock::millisToTenths, NBIT3, NBIT7, PORTA, PORTB, portHDebounce, sensorSetting::readingTimeout, Clock::realTimeClockMain, Clock::realTimeClockMillis, Clock::realTimeClockMinutes, Clock::realTimeClockSeconds, Clock::realTimeClockTenths, CoreVar::RPM, Clock::secondsToMinutes, fixedConfig2::sensorSettings, Clock::tenthsToSeconds, and Clock::timeoutADCreadingClock.

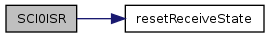

| void SCI0ISR | ( | void | ) |

Serial Communication Interface 0 ISR.

SCI0 ISR handles all interrupts for SCI0 by reading flags and acting appropriately. Its functions are to send raw bytes out over the wire from a buffer and to receive bytes from the wire un-escape them, checksum them and store them in a buffer.

- Todo:

TODO Move this code into an include file much like the fuel interrupts such that it can be used for multiple UART SCI devices without duplication.

TODO Fix the init code such that this doesn't run at boot without a serail device attached. Clear buffer maybe? or flag clearing/isr enabling ordering?

Definition at line 109 of file commsISRs.c.

References BIT4, BIT7, CLEAR_ALL_SOURCE_ID_FLAGS, COM_CLEAR_SCI0_INTERFACE_ID, COM_SET_SCI0_INTERFACE_ID, coreStatusA, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, ESCAPE_BYTE, ESCAPED_ESCAPE_BYTE, ESCAPED_START_BYTE, ESCAPED_STOP_BYTE, FLAG_AND_INC_FLAGGABLE, FLAG_SERIAL_ESCAPE_PAIR_MISMATCHES_OFFSET, FLAG_SERIAL_FRAMING_ERRORS_OFFSET, FLAG_SERIAL_NOISE_ERRORS_OFFSET, FLAG_SERIAL_OVERRUN_ERRORS_OFFSET, FLAG_SERIAL_PACKETS_OVER_LENGTH_OFFSET, FLAG_SERIAL_PARITY_ERRORS_OFFSET, FLAG_SERIAL_STARTS_INSIDE_A_PACKET_OFFSET, KeyUserDebugs, NBIT4, NBIT7, PORTB, resetReceiveState(), RX_BUFFER_SIZE, RX_READY_TO_PROCESS, RX_SCI_ESCAPED_NEXT, RX_SCI_NOT_ESCAPED_NEXT, RXBufferContentSourceID, RXBufferCurrentPosition, RXStateFlags, SCI0CR2, SCI0DRL, SCI0SR1, SCICR2_RX_ISR_DISABLE, SCICR2_RX_ISR_ENABLE, SCICR2_TX_DISABLE, SCICR2_TX_ISR_DISABLE, SCICR2_TX_ISR_ENABLE, SCISR1_RX_FRAMING, SCISR1_RX_NOISE, SCISR1_RX_OVERRUN, SCISR1_RX_PARITY, SCISR1_RX_REGISTER_FULL, SCISR1_TX_REGISTER_EMPTY, KeyUserDebug::serialAndCommsCodeErrors, KeyUserDebug::serialHardwareErrors, KeyUserDebug::serialOverrunErrors, START_BYTE, STOP_BYTE, TXBufferCurrentPositionHandler, TXBufferCurrentPositionSCI0, TXBufferInUseFlags, and TXByteEscaped.

| void LowVoltageISR | ( | void | ) |

Low Voltage Counter.

Count how often our voltage drops lower than it should without resetting.

Definition at line 316 of file miscISRs.c.

References BIT6, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_LOW_VOLTAGE_CONDITION_OFFSET, NBIT6, PORTB, and VREGCTRL.

| void VRegAPIISR | ( | void | ) |

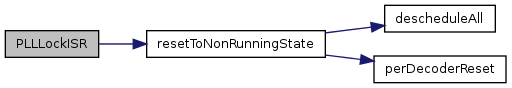

| void PLLLockISR | ( | void | ) |

PLL Lock Lost/Gained.

When the Phase Locked Loop is lost or gained, this is called.

Definition at line 111 of file miscISRs.c.

References BIT7, CRGFLG, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_PHASE_LOCKED_LOOP_LOCK_LOST_OFFSET, KeyUserDebug::ignitionCuts, KeyUserDebug::injectionCuts, KeyUserDebugs, NBIT7, PLL_LOCK_LOST_PRECAUTIONARY, PLLLOCK, PLLLOCKIF, PORTB, resetToNonRunningState(), SELF_CLOCK_MODE_PRECAUTIONARY, and KeyUserDebug::syncLostWithThisID.

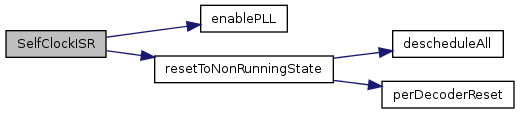

| void SelfClockISR | ( | void | ) |

Self Clock Mode Entered/Exited.

When the main clock quality drops too low to be used, self clock is entered.

See section 2.6.3 of the device manual for more information.

Definition at line 145 of file miscISRs.c.

References BIT7, CRGFLG, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, enablePLL(), FLAG_AND_INC_FLAGGABLE, FLAG_SELF_CLOCK_MODE_ENTERED_OFFSET, KeyUserDebug::ignitionCuts, KeyUserDebug::injectionCuts, KeyUserDebugs, NBIT7, PORTB, resetToNonRunningState(), SCM, SCMIF, and SELF_CLOCK_MODE_PRECAUTIONARY.

| void SpuriousISR | ( | void | ) |

Spurious Interrupt Handler.

This is fired when the correct vector for an interrupt can not be determined.

Theoretically this should not happen, and probably indicates a code fault.

Definition at line 64 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE2, FLAG_SPURIOUS_INTERRUPTS_OFFSET, NBIT7, and PORTB.

| void UnimplOpcodeISR | ( | void | ) |

Unimplemented Opcode Handler.

Unimplemented opcode trap. This should never run and probably indicates an attempt to execute data instead of code, but could be an assembler issue.

Definition at line 76 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE2, FLAG_UNIMPLEMENTED_OPCODES_OFFSET, NBIT7, and PORTB.

| void RAMViolationISR | ( | void | ) |

CPU RAM Access Violation Handler.

If the CPU tries to access protected XGATE RAM, this is fired.

Definition at line 87 of file miscISRs.c.

References AVIF, BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE2, FLAG_RAM_ACCESS_VIOLATIONS_OFFSET, NBIT7, PORTB, and RAMWPC.

| void XGATEErrorISR | ( | void | ) |

XGATE Software Error Handler.

If buggy code is being executed on the XGATE, this may fire alerting us to it.

Definition at line 99 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE2, FLAG_XGATE_SOFTWARE_ERRORS_OFFSET, NBIT7, PORTB, XGMCTL, XGSWEIF, and XGSWEIFM.

1.8.1.2

1.8.1.2