Miscellaneous Interrupt Handlers. More...

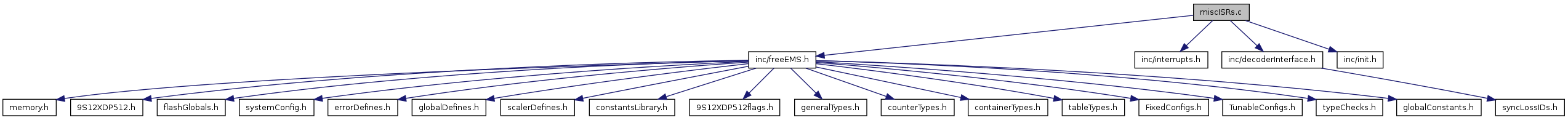

#include "inc/freeEMS.h"#include "inc/interrupts.h"#include "inc/decoderInterface.h"#include "inc/init.h"

Go to the source code of this file.

Functions | |

| void | UISR (void) |

| Unimplemented Interrupt Handler. | |

| void | SpuriousISR (void) |

| Spurious Interrupt Handler. | |

| void | UnimplOpcodeISR (void) |

| Unimplemented Opcode Handler. | |

| void | RAMViolationISR (void) |

| CPU RAM Access Violation Handler. | |

| void | XGATEErrorISR (void) |

| XGATE Software Error Handler. | |

| void | PLLLockISR (void) |

| PLL Lock Lost/Gained. | |

| void | SelfClockISR (void) |

| Self Clock Mode Entered/Exited. | |

| void | PortPISR (void) |

| Port P pins ISR. | |

| void | PortJISR (void) |

| Port J pins ISR. | |

| void | PortHISR (void) |

| Port H pins ISR. | |

| void | IRQISR (void) |

| IRQ/PE1 pin ISR. | |

| void | XIRQISR (void) |

| XIRQ/PE0 pin ISR. | |

| void | LowVoltageISR (void) |

| Low Voltage Counter. | |

Detailed Description

Miscellaneous Interrupt Handlers.

Various non-descript interrupt handlers that don't really fit anywhere else and aren't big enough to live on their own just yet.

Definition in file miscISRs.c.

Function Documentation

| void UISR | ( | void | ) |

Unimplemented Interrupt Handler.

Unimplemented interrupt service routine for calls we weren't expecting. Currently this simply counts bad calls like any other event type.

- Todo:

TODO Split this into its own file, create one for each, and clear flags for all, and increment shared counter as is.

TODO Currently not a problem, but as indirectly pointed out by johntramp, if no flag clearing is being done, then this code will run continuously, which is not a good idea...

Definition at line 52 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_CALLS_TO_UISRS_OFFSET, NBIT7, and PORTB.

| void SpuriousISR | ( | void | ) |

Spurious Interrupt Handler.

This is fired when the correct vector for an interrupt can not be determined.

Theoretically this should not happen, and probably indicates a code fault.

Definition at line 64 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE2, FLAG_SPURIOUS_INTERRUPTS_OFFSET, NBIT7, and PORTB.

| void UnimplOpcodeISR | ( | void | ) |

Unimplemented Opcode Handler.

Unimplemented opcode trap. This should never run and probably indicates an attempt to execute data instead of code, but could be an assembler issue.

Definition at line 76 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE2, FLAG_UNIMPLEMENTED_OPCODES_OFFSET, NBIT7, and PORTB.

| void RAMViolationISR | ( | void | ) |

CPU RAM Access Violation Handler.

If the CPU tries to access protected XGATE RAM, this is fired.

Definition at line 87 of file miscISRs.c.

References AVIF, BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE2, FLAG_RAM_ACCESS_VIOLATIONS_OFFSET, NBIT7, PORTB, and RAMWPC.

| void XGATEErrorISR | ( | void | ) |

XGATE Software Error Handler.

If buggy code is being executed on the XGATE, this may fire alerting us to it.

Definition at line 99 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE2, FLAG_XGATE_SOFTWARE_ERRORS_OFFSET, NBIT7, PORTB, XGMCTL, XGSWEIF, and XGSWEIFM.

| void PLLLockISR | ( | void | ) |

PLL Lock Lost/Gained.

When the Phase Locked Loop is lost or gained, this is called.

Definition at line 111 of file miscISRs.c.

References BIT7, CRGFLG, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_PHASE_LOCKED_LOOP_LOCK_LOST_OFFSET, KeyUserDebug::ignitionCuts, KeyUserDebug::injectionCuts, KeyUserDebugs, NBIT7, PLL_LOCK_LOST_PRECAUTIONARY, PLLLOCK, PLLLOCKIF, PORTB, resetToNonRunningState(), SELF_CLOCK_MODE_PRECAUTIONARY, and KeyUserDebug::syncLostWithThisID.

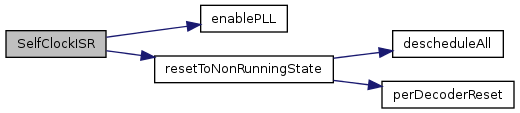

| void SelfClockISR | ( | void | ) |

Self Clock Mode Entered/Exited.

When the main clock quality drops too low to be used, self clock is entered.

See section 2.6.3 of the device manual for more information.

Definition at line 145 of file miscISRs.c.

References BIT7, CRGFLG, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, enablePLL(), FLAG_AND_INC_FLAGGABLE, FLAG_SELF_CLOCK_MODE_ENTERED_OFFSET, KeyUserDebug::ignitionCuts, KeyUserDebug::injectionCuts, KeyUserDebugs, NBIT7, PORTB, resetToNonRunningState(), SCM, SCMIF, and SELF_CLOCK_MODE_PRECAUTIONARY.

| void PortPISR | ( | void | ) |

Port P pins ISR.

Interrupt handler for edge events on port P pins. Not currently used.

Definition at line 173 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_CALLS_TO_UISRS_OFFSET, NBIT7, ONES, PIFP, and PORTB.

| void PortJISR | ( | void | ) |

Port J pins ISR.

Interrupt handler for edge events on port J pins. Not currently used.

Definition at line 186 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_CALLS_TO_UISRS_OFFSET, NBIT7, ONES, PIFJ, and PORTB.

| void PortHISR | ( | void | ) |

Port H pins ISR.

Interrupt handler for edge events on port H pins. Not currently used.

Definition at line 199 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_CALLS_TO_UISRS_OFFSET, NBIT7, ONES, PIFH, PORTB, and portHDebounce.

| void IRQISR | ( | void | ) |

IRQ/PE1 pin ISR.

Interrupt handler for edge events on the IRQ/PE1 pin. Not currently used.

Definition at line 290 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_CALLS_TO_UISRS_OFFSET, NBIT7, and PORTB.

| void XIRQISR | ( | void | ) |

XIRQ/PE0 pin ISR.

Interrupt handler for edge events on the XIRQ/PE0 pin. Not currently used.

Definition at line 303 of file miscISRs.c.

References BIT7, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_CALLS_TO_UISRS_OFFSET, NBIT7, and PORTB.

| void LowVoltageISR | ( | void | ) |

Low Voltage Counter.

Count how often our voltage drops lower than it should without resetting.

Definition at line 316 of file miscISRs.c.

References BIT6, DEBUG_TURN_PIN_OFF, DEBUG_TURN_PIN_ON, DECODER_BENCHMARKS, FLAG_AND_INC_FLAGGABLE, FLAG_LOW_VOLTAGE_CONDITION_OFFSET, NBIT6, PORTB, and VREGCTRL.

1.8.1.2

1.8.1.2