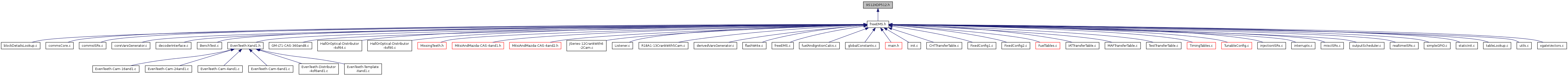

MC9S12XDP512 register definitions. More...

Go to the source code of this file.

Macros | |

| #define | DVUCP(address) (*((volatile unsigned char*)(address))) |

| #define | DVUSP(address) (*((volatile unsigned short*)(address))) |

| #define | AVUCP(address) ((volatile unsigned char*)(address)) |

| #define | AVUSP(address) ((volatile unsigned short*)(address)) |

| #define | PORTS_BA DVUSP(0x0001) |

| #define | PORTA DVUCP(0x0000) |

| #define | PORTB DVUCP(0x0001) |

| #define | PORTE DVUCP(0x0008) |

| #define | PORTK DVUCP(0x0032) |

| #define | PORTC DVUCP(0x0004) |

| #define | PORTD DVUCP(0x0005) |

| #define | DDRA DVUCP(0x0002) |

| #define | DDRB DVUCP(0x0003) |

| #define | DDRE DVUCP(0x0009) |

| #define | DDRK DVUCP(0x0033) |

| #define | DDRC DVUCP(0x0006) /* these pins are not bonded on the 112 pin package but need switching to output */ |

| #define | DDRD DVUCP(0x0007) /* these pins are not bonded on the 112 pin package but need switching to output */ |

| #define | PUCR DVUCP(0x000C) /* pull up enable when used as an input, 0 = no pull up, 1 = pull up on */ |

| #define | RDRIV DVUCP(0x000D) /* reduced drive register when used as output, 0 = full drive, 1 = reduced drive */ |

| #define | ECLKCTL DVUCP(0x001C) /* Comes up 0b_1100_0000 = both pins off in normal single chip mode */ |

| #define | IRQCR DVUCP(0x001E) /* 0 in bit 7 makes it ultra sensitive, 1 makes it falling edge sensitive. 0 in bit 6 turns interrupts off, 1 in bit 6 turns them on. */ |

| #define | PTT DVUCP(0x0240) /* GPIO output register, can not be read from reliably, use PTIT instead */ |

| #define | PORTT DVUCP(0x0240) /* Duplicate definition for consistency */ |

| #define | PTIT DVUCP(0x0241) /* read only port state bits, always return the state of the pin, can be used to detect overload on outputs */ |

| #define | DDRT DVUCP(0x0242) /* TODO configure all IO as outputs until we need it */ |

| #define | RDRT DVUCP(0x0243) /* reduced drive register when used as output, 0 = full drive, 1 = reduced drive */ |

| #define | PERT DVUCP(0x0244) /* pull up/down enable when used as an input, 0 = no pull up, 1 = pull up on */ |

| #define | PPST DVUCP(0x0245) /* 0 = pull up, 1 = pull down */ |

| #define | PTS DVUCP(0x0248) |

| #define | PORTS DVUCP(0x0248) /* Duplicate definition for consistency */ |

| #define | PTIS DVUCP(0x0249) /* read only port state bits, always return the state of the pin, can be used to detect overload on outputs */ |

| #define | DDRS DVUCP(0x024A) /* TODO configure all IO as outputs until we need it */ |

| #define | RDRS DVUCP(0x024B) /* reduced drive register when used as output, 0 = full drive, 1 = reduced drive */ |

| #define | PERS DVUCP(0x024C) /* pull up enable when used as an input, 0 = no pull up, 1 = pull up on */ |

| #define | PPSS DVUCP(0x024D) /* 0 = pull up, 1 = pull down */ |

| #define | WOMS DVUCP(0x024E) /* wired OR mode TODO find out what this actually means in real terms. */ |

| #define | PTM DVUCP(0x0250) |

| #define | PORTM DVUCP(0x0250) /* Duplicate definition for consistency */ |

| #define | PTIM DVUCP(0x0251) /* read only port state bits, always return the state of the pin, can be used to detect overload on outputs */ |

| #define | DDRM DVUCP(0x0252) /* TODO configure all IO as outputs until we need it */ |

| #define | RDRM DVUCP(0x0253) /* reduced drive register when used as output, 0 = full drive, 1 = reduced drive */ |

| #define | PERM DVUCP(0x0254) /* pull up enable when used as an input, 0 = no pull up, 1 = pull up on */ |

| #define | PPSM DVUCP(0x0255) /* 0 = pull up, 1 = pull down */ |

| #define | WOMM DVUCP(0x0256) /* wired OR mode TODO find out what this actually means in real terms. */ |

| #define | MODRR DVUCP(0x0257) |

| #define | PTP DVUCP(0x0258) |

| #define | PORTP DVUCP(0x0258) /* Duplicate definition for consistency */ |

| #define | PTIP DVUCP(0x0259) /* read only port state bits, always return the state of the pin, can be used to detect overload on outputs */ |

| #define | DDRP DVUCP(0x025A) /* TODO configure all IO as outputs until we need it */ |

| #define | RDRP DVUCP(0x025B) /* reduced drive register when used as output, 0 = full drive, 1 = reduced drive */ |

| #define | PERP DVUCP(0x025C) /* pull up enable when used as an input, 0 = no pull up, 1 = pull up on */ |

| #define | PPSP DVUCP(0x025D) /* 0 = pull up, 1 = pull down AND when IE pull down means I on rising edge and pull up means I on falling edge */ |

| #define | PIEP DVUCP(0x025E) /* interrupt enable, turns on interrupts */ |

| #define | PIFP DVUCP(0x025F) /* interrupt flag, write a 1 to clear it */ |

| #define | PTH DVUCP(0x0260) |

| #define | PORTH DVUCP(0x0260) /* Duplicate definition for consistency */ |

| #define | PTIH DVUCP(0x0261) /* read only port state bits, always return the state of the pin, can be used to detect overload on outputs */ |

| #define | DDRH DVUCP(0x0262) /* TODO configure all IO as outputs until we need it */ |

| #define | RDRH DVUCP(0x0263) /* reduced drive register when used as output, 0 = full drive, 1 = reduced drive */ |

| #define | PERH DVUCP(0x0264) /* pull up enable when used as an input, 0 = no pull up, 1 = pull up on */ |

| #define | PPSH DVUCP(0x0265) /* 0 = pull up, 1 = pull down AND when IE pull down means I on rising edge and pull up means I on falling edge */ |

| #define | PIEH DVUCP(0x0266) /* interrupt enable, turns on interrupts */ |

| #define | PIFH DVUCP(0x0267) /* interrupt flag, write a 1 to clear it */ |

| #define | PTJ DVUCP(0x0268) |

| #define | PORTJ DVUCP(0x0268) /* Duplicate definition for consistency */ |

| #define | PTIJ DVUCP(0x0269) /* read only port state bits, always return the state of the pin, can be used to detect overload on outputs */ |

| #define | DDRJ DVUCP(0x026A) /* TODO configure all IO as outputs until we need it */ |

| #define | RDRJ DVUCP(0x026B) /* reduced drive register when used as output, 0 = full drive, 1 = reduced drive */ |

| #define | PERJ DVUCP(0x026C) /* pull up enable when used as an input, 0 = no pull up, 1 = pull up on */ |

| #define | PPSJ DVUCP(0x026D) /* 0 = pull up, 1 = pull down AND when IE pull down means I on rising edge and pull up means I on falling edge */ |

| #define | PIEJ DVUCP(0x026E) /* interrupt enable, turns on interrupts */ |

| #define | PIFJ DVUCP(0x026F) /* interrupt flag, write a 1 to clear it */ |

| #define | ATD0PER1 DVUCP(0x0277) /* pull up enable when used as an input, 0 = no pull up, 1 = pull up on */ |

| #define | RPAGE DVUCP(0x0016) /* Used to page table data in and out of visible memory. */ |

| #define | PPAGE DVUCP(0x0030) /* TODO look at the best way to use the flash space in a complete system with a lot of code and data. used by compiler and maybe us to switch flash pages for loading/unloading data. */ |

| #define | RAMWPC DVUCP(0x011C) /* RAM Write Protection register, the pdf document appears to be incorrect for this, best not to touch it. */ |

| #define | RAMXGU DVUCP(0x011D) /* XGATE Upper region limit, this defines how much RAM we give the xgate to work with. */ |

| #define | RAMSHL DVUCP(0x011E) /* Shared memory lower boundary register, this defines the lower limit of the overlap between XGATE RAM and CPU RAM */ |

| #define | RAMSHU DVUCP(0x011F) /* Shared memory upper boundary register, this defines the upper limit of the overlap between XGATE RAM and CPU RAM */ |

| #define | SYNR DVUCP(0x0034) /* Multiplier of result of division by REFDV below, output is new PLL/Bus freqency. */ |

| #define | REFDV DVUCP(0x0035) /* Divisor of external clock frequency pre being multiplied by SYNR above. */ |

| #define | CRGFLG DVUCP(0x0037) /* Clock and Reset Generator flags, we use this to determine when the PLL is stable and ready to use. Also to reset the RTI flag. */ |

| #define | CRGINT DVUCP(0x0038) /* Bit 7 is RTIE RTI enable bit. */ |

| #define | CLKSEL DVUCP(0x0039) /* Clock select register, choose PLL or external clock with this. */ |

| #define | PLLCTL DVUCP(0x003A) /* PLL frequency generator control register, used for setting the bus frequency. */ |

| #define | RTICTL DVUCP(0x003B) /* Divider select register */ |

| #define | COPCTL DVUCP(0x003C) /* COP watch dog control register */ |

| #define | ARMCOP DVUCP(0x003F) /* Computer operating properly timer, we won't be using this at least until we have profiled the running application. it will just cause headaches otherwise. */ |

| #define | TCNT DVUSP(0x0044) /* Timer counter 16 bit (0x0044 TCNT (hi), 0x0045 TCNT (lo)) */ |

| #define | TIOS DVUCP(0x0040) /* Selects input capture or output compare mode for each timer pin */ |

| #define | TIE DVUCP(0x004C) /* Timer channel interrupt enable register */ |

| #define | TSCR1 DVUCP(0x0046) /* Timer System Control Register 1 */ |

| #define | TSCR2 DVUCP(0x004D) /* Timer System Control Register 2 */ |

| #define | TFLG DVUCP(0x004E) /* Timer channel flags */ |

| #define | TFLGOF DVUCP(0x004F) /* Timer over flow flag */ |

| #define | PTPSR DVUCP(0x006E) /* Precision prescaler for the main timer */ |

| #define | TTOV DVUCP(0x0047) /* Timer Toggle on Overflow output compare control */ |

| #define | CFORC DVUCP(0x0041) /* Output compare force, write a 1 to make the programmed action occur now */ |

| #define | OC7M DVUCP(0x0042) /* Channel 7 output compare other pins control mask */ |

| #define | OC7D DVUCP(0x0043) /* Channel 7 output compare other pins states */ |

| #define | TCTL1 DVUCP(0x0048) /* (M,L) 77,66,55,44 */ |

| #define | TCTL2 DVUCP(0x0049) /* (M,L) 33,22,11,00 */ |

| #define | TCTL1_ADDR AVUCP(0x0048) /* (M,L) 77,66,55,44 */ |

| #define | TCTL2_ADDR AVUCP(0x0049) /* (M,L) 33,22,11,00 */ |

| #define | DLYCT DVUCP(0x0069) /* Delay counter control register (minimum tooth width) */ |

| #define | ICSYS DVUCP(0x006B) /* Input capture behaviour control register */ |

| #define | ICOVW DVUCP(0x006A) /* Input capture overwrite allow */ |

| #define | TCTL3 DVUCP(0x004A) /* (B,A) 77,66,55,44 */ |

| #define | TCTL4 DVUCP(0x004B) /* (B,A) 33,22,11,00 */ |

| #define | TC0H DVUSP(0x0078) /* 16 bit (0x0078 TC0H (hi), 0x0079 TC0H (lo)) */ |

| #define | TC1H DVUSP(0x007A) /* 16 bit (0x007A TC1H (hi), 0x007B TC1H (lo)) */ |

| #define | TC2H DVUSP(0x007C) /* 16 bit (0x007C TC2H (hi), 0x007D TC2H (lo)) */ |

| #define | TC3H DVUSP(0x007E) /* 16 bit (0x007E TC3H (hi), 0x007F TC3H (lo)) */ |

| #define | TC0 DVUSP(0x0050) /* 16 bit (0x0050 TC0 (hi), 0x0051 TC0 (lo)) */ |

| #define | TC1 DVUSP(0x0052) /* 16 bit (0x0052 TC1 (hi), 0x0053 TC1 (lo)) */ |

| #define | TC2 DVUSP(0x0054) /* 16 bit (0x0054 TC2 (hi), 0x0055 TC2 (lo)) */ |

| #define | TC3 DVUSP(0x0056) /* 16 bit (0x0056 TC3 (hi), 0x0057 TC3 (lo)) */ |

| #define | TC4 DVUSP(0x0058) /* 16 bit (0x0058 TC4 (hi), 0x0059 TC4 (lo)) */ |

| #define | TC5 DVUSP(0x005A) /* 16 bit (0x005A TC5 (hi), 0x005B TC5 (lo)) */ |

| #define | TC6 DVUSP(0x005C) /* 16 bit (0x005C TC6 (hi), 0x005D TC6 (lo)) */ |

| #define | TC7 DVUSP(0x005E) /* 16 bit (0x005E TC7 (hi), 0x005F TC7 (lo)) */ |

| #define | TC2_ADDR AVUSP(0x0054) /* 16 bit (0x0054 TC2 (hi), 0x0055 TC2 (lo)) */ |

| #define | TC3_ADDR AVUSP(0x0056) /* 16 bit (0x0056 TC3 (hi), 0x0057 TC3 (lo)) */ |

| #define | TC4_ADDR AVUSP(0x0058) /* 16 bit (0x0058 TC4 (hi), 0x0059 TC4 (lo)) */ |

| #define | TC5_ADDR AVUSP(0x005A) /* 16 bit (0x005A TC5 (hi), 0x005B TC5 (lo)) */ |

| #define | TC6_ADDR AVUSP(0x005C) /* 16 bit (0x005C TC6 (hi), 0x005D TC6 (lo)) */ |

| #define | TC7_ADDR AVUSP(0x005E) /* 16 bit (0x005E TC7 (hi), 0x005F TC7 (lo)) */ |

| #define | ICPAR DVUCP(0x0068) |

| #define | PACTL DVUCP(0x0060) |

| #define | PAFLG DVUCP(0x0061) |

| #define | PBCTL DVUCP(0x0070) |

| #define | PBFLG DVUCP(0x0071) |

| #define | PACNUS2 DVUSP(0x0062) /* 16 bit (0x0062 PACN3, 0x0063 PACN2) */ |

| #define | PACNUS0 DVUSP(0x0064) /* 16 bit (0x0064 PACN1, 0x0065 PACN0) */ |

| #define | PACN3 DVUCP(0x0062) /* high */ |

| #define | PACN2 DVUCP(0x0063) /* low */ |

| #define | PACN1 DVUCP(0x0064) /* high */ |

| #define | PACN0 DVUCP(0x0065) /* low */ |

| #define | PACHUS2 DVUSP(0x0072) /* 16 bit (0x0072 PACH3, 0x0073 PACH2) */ |

| #define | PACHUS0 DVUSP(0x0074) /* 16 bit (0x0074 PACH1, 0x0075 PACH0) */ |

| #define | PA3H DVUCP(0x0072) /* high */ |

| #define | PA2H DVUCP(0x0073) /* low */ |

| #define | PA1H DVUCP(0x0074) /* high */ |

| #define | PA0H DVUCP(0x0075) /* low */ |

| #define | MCCTL DVUCP(0x0066) /* Modulus control register */ |

| #define | MCFLG DVUCP(0x0067) /* Modulus flag (high bit) and input edge indicators (low 4 bits) */ |

| #define | MCCNT DVUSP(0x0076) /* 16 bit (0x0076 MCCNT (hi), 0x0077 MCCNT (lo)) */ |

| #define | PTMCPSR DVUCP(0x006F) /* Precision prescaler for the modulus down counter */ |

| #define | ATD1CTL0 DVUCP(0x0080) /* 0 - 3 define which ADC channel to wrap on when doing multiple channels */ |

| #define | ATD1CTL1 DVUCP(0x0081) /* External trigger select when enabled in other control register */ |

| #define | ATD1CTL2 DVUCP(0x0082) /* bit 7 turns the ADC block on. */ |

| #define | ATD1CTL3 DVUCP(0x0083) /* bit 6 means conversion length is 8, bit 2 controls how the registers are used, bits 0 - 1 define freeze mode behaviour */ |

| #define | ATD1CTL4 DVUCP(0x0084) /* bit 7 should be zero meaning 10bit ADC, bits 6,5 are the sample period, and 4,3,2,1,0 are the sample frequency clock scaler */ |

| #define | ATD1CTL5 DVUCP(0x0085) /* bit 7 sets right justify, bit 5 sets scan mode, bit 4 sets multiplex mode */ |

| #define | ATD1DIEN0 DVUCP(0x008C) /* Digital input enable - these pins are not bonded on the 112 pin package */ |

| #define | ATD1DIEN1 DVUCP(0x008D) /* Digital input enable */ |

| #define | ATD1_BASE 0x0090 |

| #define | ATD1DR0 DVUSP(ATD1_BASE + 0x0) /* 16 bit (0x0090 ATD1DR0H, 0x0091 ATD1DR0L) */ /* SpareADC (NC) */ |

| #define | ATD1DR1 DVUSP(ATD1_BASE + 0x2) /* 16 bit (0x0092 ATD1DR1H, 0x0093 ATD1DR1L) */ /* SpareADC (NC) */ |

| #define | ATD1DR2 DVUSP(ATD1_BASE + 0x4) /* 16 bit (0x0094 ATD1DR2H, 0x0095 ATD1DR2L) */ /* SpareADC (NC) */ |

| #define | ATD1DR3 DVUSP(ATD1_BASE + 0x6) /* 16 bit (0x0096 ATD1DR3H, 0x0097 ATD1DR3L) */ /* SpareADC (NC) */ |

| #define | ATD1DR4 DVUSP(ATD1_BASE + 0x8) /* 16 bit (0x0098 ATD1DR4H, 0x0099 ATD1DR4L) */ /* SpareADC (NC) */ |

| #define | ATD1DR5 DVUSP(ATD1_BASE + 0xA) /* 16 bit (0x009A ATD1DR5H, 0x009B ATD1DR5L) */ /* SpareADC (NC) */ |

| #define | ATD1DR6 DVUSP(ATD1_BASE + 0xC) /* 16 bit (0x009C ATD1DR6H, 0x009D ATD1DR6L) */ /* SpareADC (NC) */ |

| #define | ATD1DR7 DVUSP(ATD1_BASE + 0xE) /* 16 bit (0x009E ATD1DR7H, 0x009F ATD1DR7L) */ /* SpareADC (NC) */ |

| #define | SCI0_BASE 0x00C8 |

| #define | SCI0BD DVUSP(SCI0_BASE + 0x0) /* #define SCI0BDH DVUCP(0x00C8), #define SCI0BDL DVUCP(0x00C9) (IR and baud control) */ |

| #define | SCI0CR1 DVUCP(SCI0_BASE + 0x2) /* Control reg 1 */ |

| #define | SCI0ASR1 DVUCP(SCI0_BASE + 0x0) /* Status reg 1a (rx flags) */ |

| #define | SCI0ACR1 DVUCP(SCI0_BASE + 0x1) /* Control reg 1a (rx conf) */ |

| #define | SCI0ACR2 DVUCP(SCI0_BASE + 0x2) /* Control reg 2a (rx conf) */ |

| #define | SCI0CR2 DVUCP(SCI0_BASE + 0x3) /* Control reg 2 */ |

| #define | SCI0SR1 DVUCP(SCI0_BASE + 0x4) /* Status reg 1 (isr flags) */ |

| #define | SCI0SR2 DVUCP(SCI0_BASE + 0x5) /* Status reg 2 (config/control) */ |

| #define | SCI0DRH DVUCP(SCI0_BASE + 0x6) /* Data reg high (9th bit bit 7 receive bit 6 send) */ |

| #define | SCI0DRL DVUCP(SCI0_BASE + 0x7) /* Data reg low (read and write for receive and send respectively)*/ |

| #define | SPI0CR1 DVUCP(0x00D8) |

| #define | SPI0CR2 DVUCP(0x00D9) |

| #define | SPI0BR DVUCP(0x00DA) |

| #define | SPI0SR DVUCP(0x00DB) |

| #define | SPI0DR DVUCP(0x00DD) |

| #define | FCLKDIV DVUCP(0x0100) /* Flash Clock Divider Register R/W */ |

| #define | FSEC DVUCP(0x0101) /* Flash Security Register R */ |

| #define | FCNFG DVUCP(0x0103) /* Flash Configuration Register R/W */ |

| #define | FPROT DVUCP(0x0104) /* Flash Protection Register R/W */ |

| #define | FSTAT DVUCP(0x0105) /* Flash Status Register R/W */ |

| #define | FCMD DVUCP(0x0106) /* Flash Command Register R/W */ |

| #define | FCTL DVUCP(0x0107) /* Flash Control Register R */ |

| #define | FADDR DVUSP(0x0108) /* Flash Low Address Register R (0x0108 FADDRHI, 0x0109 FADDRLO) */ |

| #define | FDATA DVUSP(0x010A) /* Flash High Data Register R (0x010A FDATAHI, 0x010B FDATALO) */ |

| #define | IVBR DVUCP(0x0121) /* Interrupt vector table base location first byte (second is always 0x00) */ |

| #define | INT_XGPRIO DVUCP(0x0126) |

| #define | INT_CFADDR DVUCP(0x0127) |

| #define | INT_CFDATA0 DVUCP(0x0128) |

| #define | INT_CFDATA_ARR AVUCP(0x0128) |

| #define | INT_CFDATA1 DVUCP(0x0129) |

| #define | INT_CFDATA2 DVUCP(0x012A) |

| #define | INT_CFDATA3 DVUCP(0x012B) |

| #define | INT_CFDATA4 DVUCP(0x012C) |

| #define | INT_CFDATA5 DVUCP(0x012D) |

| #define | INT_CFDATA6 DVUCP(0x012E) |

| #define | INT_CFDATA7 DVUCP(0x012F) |

| #define | CAN0CTL1 DVUCP(0x0141) |

| #define | CAN1CTL1 DVUCP(0x0181) |

| #define | CAN3CTL1 DVUCP(0x0201) |

| #define | CAN4CTL1 DVUCP(0x0281) |

| #define | ATD0CTL0 DVUCP(0x02C0) /* 0 - 2 define which ADC channel to wrap on when doing multiple channels */ |

| #define | ATD0CTL1 DVUCP(0x02C1) /* External trigger select when enabled in other control register */ |

| #define | ATD0CTL2 DVUCP(0x02C2) /* bit 7 turns the ADC block on. */ |

| #define | ATD0CTL3 DVUCP(0x02C3) /* bit 6 means conversion length is 8, bit 2 controls how the registers are used, bits 0 - 1 define freeze mode behaviour */ |

| #define | ATD0CTL4 DVUCP(0x02C4) /* bit 7 should be zero meaning 10bit ADC, bits 6,5 are the sample period, and 4,3,2,1,0 are the sample frequency clock scaler */ |

| #define | ATD0CTL5 DVUCP(0x02C5) /* bit 7 sets right justify, bit 5 sets scan mode, bit 4 sets multiplex mode */ |

| #define | ATD0DIEN DVUCP(0x02CD) /* Digital input enable */ |

| #define | ATD0_BASE 0x02D0 /* Maybe use this with a loop to sample them in a compact way. */ |

| #define | ATD0DR0 DVUSP(ATD0_BASE + 0x0) /* 16 bit (0x02D0 ATD0DR0H, 0x02D1 ATD0DR0L) */ |

| #define | ATD0DR1 DVUSP(ATD0_BASE + 0x2) /* 16 bit (0x02D2 ATD0DR1H, 0x02D3 ATD0DR1L) */ |

| #define | ATD0DR2 DVUSP(ATD0_BASE + 0x4) /* 16 bit (0x02D4 ATD0DR2H, 0x02D5 ATD0DR2L) */ |

| #define | ATD0DR3 DVUSP(ATD0_BASE + 0x6) /* 16 bit (0x02D6 ATD0DR3H, 0x02D7 ATD0DR3L) */ |

| #define | ATD0DR4 DVUSP(ATD0_BASE + 0x8) /* 16 bit (0x02D8 ATD0DR4H, 0x02D9 ATD0DR4L) */ |

| #define | ATD0DR5 DVUSP(ATD0_BASE + 0xA) /* 16 bit (0x02DA ATD0DR5H, 0x02DB ATD0DR5L) */ |

| #define | ATD0DR6 DVUSP(ATD0_BASE + 0xC) /* 16 bit (0x02DC ATD0DR6H, 0x02DD ATD0DR6L) */ |

| #define | ATD0DR7 DVUSP(ATD0_BASE + 0xE) /* 16 bit (0x02DE ATD0DR7H, 0x02DF ATD0DR7L) */ |

| #define | VREGCTRL DVUCP(0x02F1) /* VReg Control Register */ |

| #define | VREGAPICL DVUCP(0x02F2) /* Autonomous Periodical Interrupt Control Register */ |

| #define | VREGAPITR DVUCP(0x02F3) /* Autonomous Periodical Interrupt Trimming Register */ |

| #define | VREGAPIR DVUSP(0x02F4) /* Autonomous Periodical Interrupt Rate High and Low Registers (VREGAPIRH DVUCP(0x02F4), VREGAPIRL DVUCP(0x02F5)) */ |

| #define | PWME DVUCP(0x0300) /* PWM enable register */ |

| #define | PWMPOL DVUCP(0x0301) /* PWM polarity register */ |

| #define | PWMCLK DVUCP(0x0302) /* PWM clock choice register */ |

| #define | PWMPRCLK DVUCP(0x0303) /* PWM Clock prescalers (bits 0,1,2 and bits 4,5,6 control 4 pins each) */ |

| #define | PWMCAE DVUCP(0x0304) /* PWM Center Align Enable Register */ |

| #define | PWMCTL DVUCP(0x0305) /* PWM Concatenate, stop, wait, freeze register */ |

| #define | PWMSCLA DVUCP(0x0308) /* PWM Scale A register */ |

| #define | PWMSCLB DVUCP(0x0309) /* PWM Scale B register */ |

| #define | PWMCNT0 DVUCP(0x030C) /* PWM 8 bit counter */ |

| #define | PWMCNT1 DVUCP(0x030D) /* */ |

| #define | PWMCNT2 DVUCP(0x030E) /* */ |

| #define | PWMCNT3 DVUCP(0x030F) /* */ |

| #define | PWMCNT4 DVUCP(0x0310) /* */ |

| #define | PWMCNT5 DVUCP(0x0311) /* */ |

| #define | PWMCNT6 DVUCP(0x0312) /* */ |

| #define | PWMCNT7 DVUCP(0x0313) /* PWM 8 bit counter */ |

| #define | PWMPER0 DVUCP(0x0314) /* PWM period value */ |

| #define | PWMPER1 DVUCP(0x0315) /* */ |

| #define | PWMPER2 DVUCP(0x0316) /* */ |

| #define | PWMPER3 DVUCP(0x0317) /* */ |

| #define | PWMPER4 DVUCP(0x0318) /* */ |

| #define | PWMPER5 DVUCP(0x0319) /* */ |

| #define | PWMPER6 DVUCP(0x031A) /* */ |

| #define | PWMPER7 DVUCP(0x031B) /* PWM period value */ |

| #define | PWMDTY0 DVUCP(0x031C) /* PWM duty cycle value */ |

| #define | PWMDTY1 DVUCP(0x031D) /* */ |

| #define | PWMDTY2 DVUCP(0x031E) /* */ |

| #define | PWMDTY3 DVUCP(0x031F) /* */ |

| #define | PWMDTY4 DVUCP(0x0320) /* */ |

| #define | PWMDTY5 DVUCP(0x0321) /* */ |

| #define | PWMDTY6 DVUCP(0x0322) /* */ |

| #define | PWMDTY7 DVUCP(0x0323) /* PWM duty cycle value */ |

| #define | PWMSDN DVUCP(0x0324) /* PWM shutdown behaviour register */ |

| #define | PITCFLMT DVUCP(0x0340) /* PIT Control and Force Load Micro Timer Register, high bit enables, low 2 bits force load micro timers */ |

| #define | PITFLT DVUCP(0x0341) /* PIT Force Load Timer Register, low 4 bits force load timers */ |

| #define | PITCE DVUCP(0x0342) /* PIT Channel Enable Register, low 4 bits let the channel count */ |

| #define | PITMUX DVUCP(0x0343) /* PIT Multiplex Register, low 4 bits set which micro time base is used */ |

| #define | PITINTE DVUCP(0x0344) /* PIT Interrupt Enable Register, low four bits control the ISRs */ |

| #define | PITTF DVUCP(0x0345) /* PIT Time-Out Flag Register, low 4 bits set when each counter reaches 0 */ |

| #define | PITMTLD0 DVUCP(0x0346) /* PIT Micro Timer Load Register 0, time to start counting from when reaching zero */ |

| #define | PITMTLD1 DVUCP(0x0347) /* PIT Micro Timer Load Register 1, time to start counting from when reaching zero */ |

| #define | PITLD0 DVUSP(0x0348) /* PIT Load Register 0, time to start counting from when reaching zero (0x0348 PITLD0 (hi), 0x0349 PITLD0 (lo)) */ |

| #define | PITLD1 DVUSP(0x034C) /* PIT Load Register 1, time to start counting from when reaching zero (0x034C PITLD1 (hi), 0x034D PITLD1 (lo)) */ |

| #define | PITLD2 DVUSP(0x0350) /* PIT Load Register 2, time to start counting from when reaching zero (0x0350 PITLD2 (hi), 0x0351 PITLD2 (lo)) */ |

| #define | PITLD3 DVUSP(0x0354) /* PIT Load Register 3, time to start counting from when reaching zero (0x0354 PITLD3 (hi), 0x0355 PITLD3 (lo)) */ |

| #define | PITCNT0 DVUSP(0x034A) /* PIT Count Register 0, current value of down counter (0x034A PITCNT0 (hi), 0x034B PITCNT0 (lo)) */ |

| #define | PITCNT1 DVUSP(0x034E) /* PIT Count Register 1, current value of down counter (0x034E PITCNT1 (hi), 0x034F PITCNT1 (lo)) */ |

| #define | PITCNT2 DVUSP(0x0352) /* PIT Count Register 2, current value of down counter (0x0352 PITCNT2 (hi), 0x0353 PITCNT2 (lo)) */ |

| #define | PITCNT3 DVUSP(0x0356) /* PIT Count Register 3, current value of down counter (0x0356 PITCNT3 (hi), 0x0357 PITCNT3 (lo)) */ |

| #define | XGMCTL DVUSP(0x0380) |

| #define | XGMCTLHI DVUCP(0x0380) |

| #define | XGMCTLLO DVUCP(0x0381) |

| #define | XGCHID DVUCP(0x0382) |

| #define | XGVBR DVUSP(0x0386) /* This is all that is used on the xdp512! 16 bit (0x0386 DVUCP (hi), 0x0387 DVUCP (lo)) */ |

| #define | XGIF_0 DVUCP(0x0388) |

| #define | XGIF_1 DVUCP(0x0389) |

| #define | XGIF_2 DVUCP(0x038A) |

| #define | XGIF_3 DVUCP(0x038B) /* WRONG value 0x023B stated in the manual as being both xgate and can3!!!!! should be 0x038B i believe!!!!! */ |

| #define | XGIF_4 DVUCP(0x038C) /* WRONG value 0x023C stated in the manual as being both xgate and can3!!!!! should be 0x038C i believe!!!!! */ |

| #define | XGIF_5 DVUCP(0x038D) |

| #define | XGIF_6 DVUCP(0x038E) |

| #define | XGIF_7 DVUCP(0x038F) |

| #define | XGIF_8 DVUCP(0x0390) |

| #define | XGIF_9 DVUCP(0x0391) |

| #define | XGIF_A DVUCP(0x0392) |

| #define | XGIF_B DVUCP(0x0393) |

| #define | XGIF_C DVUCP(0x0394) |

| #define | XGIF_D DVUCP(0x0395) |

| #define | XGIF_E DVUCP(0x0396) |

| #define | XGIF_F DVUCP(0x0397) |

| #define | XGSWT DVUSP(0x0398) |

| #define | XGSEM DVUSP(0x039A) |

| #define | XGCCR DVUCP(0x039D) |

| #define | XGPC DVUSP(0x039E) |

| #define | XGR1 DVUSP(0x03A2) |

| #define | XGR2 DVUSP(0x03A4) |

| #define | XGR3 DVUSP(0x03A6) |

| #define | XGR4 DVUSP(0x03A8) |

| #define | XGR5 DVUSP(0x03AA) |

| #define | XGR6 DVUSP(0x03AC) |

| #define | XGR7 DVUSP(0x03AE) |

Detailed Description

MC9S12XDP512 register definitions.

This is the device header for the FreeScale MC9S12XDP512 MCU. It contains declarations that allow access to all of the devices control registers.

These are the full basic register definitions for the Freescale 9S12XDP512 processor as taken from MC9S12XDP512V2.pdf Appendix G

Definition in file 9S12XDP512.h.

Macro Definition Documentation

| #define DVUCP | ( | address | ) | (*((volatile unsigned char*)(address))) |

Definition at line 53 of file 9S12XDP512.h.

| #define DVUSP | ( | address | ) | (*((volatile unsigned short*)(address))) |

Definition at line 55 of file 9S12XDP512.h.

Referenced by sampleLoopADC().

| #define AVUCP | ( | address | ) | ((volatile unsigned char*)(address)) |

Definition at line 58 of file 9S12XDP512.h.

| #define AVUSP | ( | address | ) | ((volatile unsigned short*)(address)) |

Definition at line 60 of file 9S12XDP512.h.

| #define PORTS_BA DVUSP(0x0001) |

Definition at line 68 of file 9S12XDP512.h.

| #define PORTA DVUCP(0x0000) |

Definition at line 69 of file 9S12XDP512.h.

Referenced by initGPIO(), and RTIISR().

| #define PORTB DVUCP(0x0001) |

Definition at line 70 of file 9S12XDP512.h.

Referenced by initGPIO(), InjectorXISR(), IRQISR(), LowVoltageISR(), PLLLockISR(), PortHISR(), PortJISR(), PortPISR(), PrimaryRPMISR(), RAMViolationISR(), RTIISR(), SCI0ISR(), SecondaryRPMISR(), SelfClockISR(), SpuriousISR(), TimerOverflow(), UISR(), UnimplOpcodeISR(), XGATEErrorISR(), and XIRQISR().

| #define PORTE DVUCP(0x0008) |

Definition at line 71 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define PORTK DVUCP(0x0032) |

Definition at line 72 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define PORTC DVUCP(0x0004) |

Definition at line 73 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define PORTD DVUCP(0x0005) |

Definition at line 74 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define DDRA DVUCP(0x0002) |

Definition at line 78 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define DDRB DVUCP(0x0003) |

Definition at line 79 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define DDRE DVUCP(0x0009) |

Definition at line 80 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define DDRK DVUCP(0x0033) |

Definition at line 81 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define DDRC DVUCP(0x0006) /* these pins are not bonded on the 112 pin package but need switching to output */ |

Definition at line 84 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define DDRD DVUCP(0x0007) /* these pins are not bonded on the 112 pin package but need switching to output */ |

Definition at line 85 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define PUCR DVUCP(0x000C) /* pull up enable when used as an input, 0 = no pull up, 1 = pull up on */ |

Definition at line 92 of file 9S12XDP512.h.

| #define RDRIV DVUCP(0x000D) /* reduced drive register when used as output, 0 = full drive, 1 = reduced drive */ |

Definition at line 98 of file 9S12XDP512.h.

| #define ECLKCTL DVUCP(0x001C) /* Comes up 0b_1100_0000 = both pins off in normal single chip mode */ |

Definition at line 101 of file 9S12XDP512.h.

| #define IRQCR DVUCP(0x001E) /* 0 in bit 7 makes it ultra sensitive, 1 makes it falling edge sensitive. 0 in bit 6 turns interrupts off, 1 in bit 6 turns them on. */ |

Definition at line 102 of file 9S12XDP512.h.

| #define PTT DVUCP(0x0240) /* GPIO output register, can not be read from reliably, use PTIT instead */ |

Definition at line 106 of file 9S12XDP512.h.

| #define PORTT DVUCP(0x0240) /* Duplicate definition for consistency */ |

Definition at line 107 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define PTIT DVUCP(0x0241) /* read only port state bits, always return the state of the pin, can be used to detect overload on outputs */ |

Definition at line 108 of file 9S12XDP512.h.

Referenced by InjectorXISR(), main(), PrimaryRPMISR(), and SecondaryRPMISR().

| #define DDRT DVUCP(0x0242) /* TODO configure all IO as outputs until we need it */ |

Definition at line 109 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define RDRT DVUCP(0x0243) /* reduced drive register when used as output, 0 = full drive, 1 = reduced drive */ |

Definition at line 110 of file 9S12XDP512.h.

| #define PERT DVUCP(0x0244) /* pull up/down enable when used as an input, 0 = no pull up, 1 = pull up on */ |

Definition at line 111 of file 9S12XDP512.h.

| #define PPST DVUCP(0x0245) /* 0 = pull up, 1 = pull down */ |

Definition at line 112 of file 9S12XDP512.h.

| #define PTS DVUCP(0x0248) |

Definition at line 116 of file 9S12XDP512.h.

| #define PORTS DVUCP(0x0248) /* Duplicate definition for consistency */ |

Definition at line 117 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define PTIS DVUCP(0x0249) /* read only port state bits, always return the state of the pin, can be used to detect overload on outputs */ |

Definition at line 118 of file 9S12XDP512.h.

| #define DDRS DVUCP(0x024A) /* TODO configure all IO as outputs until we need it */ |

Definition at line 119 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define RDRS DVUCP(0x024B) /* reduced drive register when used as output, 0 = full drive, 1 = reduced drive */ |

Definition at line 120 of file 9S12XDP512.h.

| #define PERS DVUCP(0x024C) /* pull up enable when used as an input, 0 = no pull up, 1 = pull up on */ |

Definition at line 121 of file 9S12XDP512.h.

| #define PPSS DVUCP(0x024D) /* 0 = pull up, 1 = pull down */ |

Definition at line 122 of file 9S12XDP512.h.

| #define WOMS DVUCP(0x024E) /* wired OR mode TODO find out what this actually means in real terms. */ |

Definition at line 123 of file 9S12XDP512.h.

| #define PTM DVUCP(0x0250) |

Definition at line 127 of file 9S12XDP512.h.

| #define PORTM DVUCP(0x0250) /* Duplicate definition for consistency */ |

Definition at line 128 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define PTIM DVUCP(0x0251) /* read only port state bits, always return the state of the pin, can be used to detect overload on outputs */ |

Definition at line 129 of file 9S12XDP512.h.

| #define DDRM DVUCP(0x0252) /* TODO configure all IO as outputs until we need it */ |

Definition at line 130 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define RDRM DVUCP(0x0253) /* reduced drive register when used as output, 0 = full drive, 1 = reduced drive */ |

Definition at line 131 of file 9S12XDP512.h.

| #define PERM DVUCP(0x0254) /* pull up enable when used as an input, 0 = no pull up, 1 = pull up on */ |

Definition at line 132 of file 9S12XDP512.h.

| #define PPSM DVUCP(0x0255) /* 0 = pull up, 1 = pull down */ |

Definition at line 133 of file 9S12XDP512.h.

| #define WOMM DVUCP(0x0256) /* wired OR mode TODO find out what this actually means in real terms. */ |

Definition at line 134 of file 9S12XDP512.h.

| #define MODRR DVUCP(0x0257) |

Definition at line 138 of file 9S12XDP512.h.

| #define PTP DVUCP(0x0258) |

Definition at line 142 of file 9S12XDP512.h.

| #define PORTP DVUCP(0x0258) /* Duplicate definition for consistency */ |

Definition at line 143 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define PTIP DVUCP(0x0259) /* read only port state bits, always return the state of the pin, can be used to detect overload on outputs */ |

Definition at line 144 of file 9S12XDP512.h.

| #define DDRP DVUCP(0x025A) /* TODO configure all IO as outputs until we need it */ |

Definition at line 145 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define RDRP DVUCP(0x025B) /* reduced drive register when used as output, 0 = full drive, 1 = reduced drive */ |

Definition at line 146 of file 9S12XDP512.h.

| #define PERP DVUCP(0x025C) /* pull up enable when used as an input, 0 = no pull up, 1 = pull up on */ |

Definition at line 147 of file 9S12XDP512.h.

| #define PPSP DVUCP(0x025D) /* 0 = pull up, 1 = pull down AND when IE pull down means I on rising edge and pull up means I on falling edge */ |

Definition at line 148 of file 9S12XDP512.h.

| #define PIEP DVUCP(0x025E) /* interrupt enable, turns on interrupts */ |

Definition at line 149 of file 9S12XDP512.h.

| #define PIFP DVUCP(0x025F) /* interrupt flag, write a 1 to clear it */ |

Definition at line 150 of file 9S12XDP512.h.

Referenced by PortPISR().

| #define PTH DVUCP(0x0260) |

Definition at line 154 of file 9S12XDP512.h.

| #define PORTH DVUCP(0x0260) /* Duplicate definition for consistency */ |

Definition at line 155 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define PTIH DVUCP(0x0261) /* read only port state bits, always return the state of the pin, can be used to detect overload on outputs */ |

Definition at line 156 of file 9S12XDP512.h.

| #define DDRH DVUCP(0x0262) /* TODO configure all IO as outputs until we need it */ |

Definition at line 157 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define RDRH DVUCP(0x0263) /* reduced drive register when used as output, 0 = full drive, 1 = reduced drive */ |

Definition at line 158 of file 9S12XDP512.h.

| #define PERH DVUCP(0x0264) /* pull up enable when used as an input, 0 = no pull up, 1 = pull up on */ |

Definition at line 159 of file 9S12XDP512.h.

| #define PPSH DVUCP(0x0265) /* 0 = pull up, 1 = pull down AND when IE pull down means I on rising edge and pull up means I on falling edge */ |

Definition at line 160 of file 9S12XDP512.h.

Referenced by initInterrupts().

| #define PIEH DVUCP(0x0266) /* interrupt enable, turns on interrupts */ |

Definition at line 161 of file 9S12XDP512.h.

Referenced by initInterrupts().

| #define PIFH DVUCP(0x0267) /* interrupt flag, write a 1 to clear it */ |

Definition at line 162 of file 9S12XDP512.h.

Referenced by initInterrupts(), and PortHISR().

| #define PTJ DVUCP(0x0268) |

Definition at line 166 of file 9S12XDP512.h.

| #define PORTJ DVUCP(0x0268) /* Duplicate definition for consistency */ |

Definition at line 167 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define PTIJ DVUCP(0x0269) /* read only port state bits, always return the state of the pin, can be used to detect overload on outputs */ |

Definition at line 168 of file 9S12XDP512.h.

| #define DDRJ DVUCP(0x026A) /* TODO configure all IO as outputs until we need it */ |

Definition at line 169 of file 9S12XDP512.h.

Referenced by initGPIO().

| #define RDRJ DVUCP(0x026B) /* reduced drive register when used as output, 0 = full drive, 1 = reduced drive */ |

Definition at line 170 of file 9S12XDP512.h.

| #define PERJ DVUCP(0x026C) /* pull up enable when used as an input, 0 = no pull up, 1 = pull up on */ |

Definition at line 171 of file 9S12XDP512.h.

| #define PPSJ DVUCP(0x026D) /* 0 = pull up, 1 = pull down AND when IE pull down means I on rising edge and pull up means I on falling edge */ |

Definition at line 172 of file 9S12XDP512.h.

| #define PIEJ DVUCP(0x026E) /* interrupt enable, turns on interrupts */ |

Definition at line 173 of file 9S12XDP512.h.

| #define PIFJ DVUCP(0x026F) /* interrupt flag, write a 1 to clear it */ |

Definition at line 174 of file 9S12XDP512.h.

Referenced by PortJISR().

| #define ATD0PER1 DVUCP(0x0277) /* pull up enable when used as an input, 0 = no pull up, 1 = pull up on */ |

Definition at line 180 of file 9S12XDP512.h.

| #define RPAGE DVUCP(0x0016) /* Used to page table data in and out of visible memory. */ |

Definition at line 202 of file 9S12XDP512.h.

Referenced by decodePacketAndRespond(), initPagedRAMFuel(), initPagedRAMTime(), initPagedRAMTune(), lookupMainTable(), setupPagedRAM(), writeBlock(), and writeSector().

| #define PPAGE DVUCP(0x0030) /* TODO look at the best way to use the flash space in a complete system with a lot of code and data. used by compiler and maybe us to switch flash pages for loading/unloading data. */ |

Definition at line 204 of file 9S12XDP512.h.

Referenced by decodePacketAndRespond(), eraseSector(), lookupBlockDetails(), writeBlock(), and writeSector().

| #define RAMWPC DVUCP(0x011C) /* RAM Write Protection register, the pdf document appears to be incorrect for this, best not to touch it. */ |

Definition at line 210 of file 9S12XDP512.h.

Referenced by initInterrupts(), and RAMViolationISR().

| #define RAMXGU DVUCP(0x011D) /* XGATE Upper region limit, this defines how much RAM we give the xgate to work with. */ |

Definition at line 211 of file 9S12XDP512.h.

| #define RAMSHL DVUCP(0x011E) /* Shared memory lower boundary register, this defines the lower limit of the overlap between XGATE RAM and CPU RAM */ |

Definition at line 212 of file 9S12XDP512.h.

| #define RAMSHU DVUCP(0x011F) /* Shared memory upper boundary register, this defines the upper limit of the overlap between XGATE RAM and CPU RAM */ |

Definition at line 213 of file 9S12XDP512.h.

| #define SYNR DVUCP(0x0034) /* Multiplier of result of division by REFDV below, output is new PLL/Bus freqency. */ |

Definition at line 227 of file 9S12XDP512.h.

Referenced by initPLL().

| #define REFDV DVUCP(0x0035) /* Divisor of external clock frequency pre being multiplied by SYNR above. */ |

Definition at line 228 of file 9S12XDP512.h.

Referenced by initPLL().

| #define CRGFLG DVUCP(0x0037) /* Clock and Reset Generator flags, we use this to determine when the PLL is stable and ready to use. Also to reset the RTI flag. */ |

Definition at line 230 of file 9S12XDP512.h.

Referenced by enablePLL(), initInterrupts(), PLLLockISR(), RTIISR(), and SelfClockISR().

| #define CRGINT DVUCP(0x0038) /* Bit 7 is RTIE RTI enable bit. */ |

Definition at line 231 of file 9S12XDP512.h.

Referenced by initInterrupts().

| #define CLKSEL DVUCP(0x0039) /* Clock select register, choose PLL or external clock with this. */ |

Definition at line 232 of file 9S12XDP512.h.

Referenced by enablePLL(), and initPLL().

| #define PLLCTL DVUCP(0x003A) /* PLL frequency generator control register, used for setting the bus frequency. */ |

Definition at line 233 of file 9S12XDP512.h.

Referenced by initPLL().

| #define RTICTL DVUCP(0x003B) /* Divider select register */ |

Definition at line 234 of file 9S12XDP512.h.

Referenced by initInterrupts().

| #define COPCTL DVUCP(0x003C) /* COP watch dog control register */ |

Definition at line 235 of file 9S12XDP512.h.

Referenced by decodePacketAndRespond().

| #define ARMCOP DVUCP(0x003F) /* Computer operating properly timer, we won't be using this at least until we have profiled the running application. it will just cause headaches otherwise. */ |

Definition at line 237 of file 9S12XDP512.h.

Referenced by decodePacketAndRespond().

| #define TCNT DVUSP(0x0044) /* Timer counter 16 bit (0x0044 TCNT (hi), 0x0045 TCNT (lo)) */ |

Definition at line 244 of file 9S12XDP512.h.

Referenced by InjectorXISR(), and main().

| #define TIOS DVUCP(0x0040) /* Selects input capture or output compare mode for each timer pin */ |

Definition at line 247 of file 9S12XDP512.h.

Referenced by decoderInitPreliminary(), and initECTTimer().

| #define TIE DVUCP(0x004C) /* Timer channel interrupt enable register */ |

Definition at line 248 of file 9S12XDP512.h.

Referenced by decodePacketAndRespond(), decoderInitPreliminary(), initECTTimer(), InjectorXISR(), PrimaryRPMISR(), and schedulePortTPin().

| #define TSCR1 DVUCP(0x0046) /* Timer System Control Register 1 */ |

Definition at line 249 of file 9S12XDP512.h.

Referenced by initECTTimer().

| #define TSCR2 DVUCP(0x004D) /* Timer System Control Register 2 */ |

Definition at line 250 of file 9S12XDP512.h.

Referenced by initECTTimer().

| #define TFLG DVUCP(0x004E) /* Timer channel flags */ |

Definition at line 251 of file 9S12XDP512.h.

Referenced by initECTTimer(), InjectorXISR(), PrimaryRPMISR(), and SecondaryRPMISR().

| #define TFLGOF DVUCP(0x004F) /* Timer over flow flag */ |

Definition at line 252 of file 9S12XDP512.h.

Referenced by initECTTimer(), InjectorXISR(), main(), PrimaryRPMISR(), SecondaryRPMISR(), and TimerOverflow().

| #define PTPSR DVUCP(0x006E) /* Precision prescaler for the main timer */ |

Definition at line 253 of file 9S12XDP512.h.

Referenced by initECTTimer().

| #define TTOV DVUCP(0x0047) /* Timer Toggle on Overflow output compare control */ |

Definition at line 256 of file 9S12XDP512.h.

| #define CFORC DVUCP(0x0041) /* Output compare force, write a 1 to make the programmed action occur now */ |

Definition at line 257 of file 9S12XDP512.h.

| #define OC7M DVUCP(0x0042) /* Channel 7 output compare other pins control mask */ |

Definition at line 258 of file 9S12XDP512.h.

| #define OC7D DVUCP(0x0043) /* Channel 7 output compare other pins states */ |

Definition at line 259 of file 9S12XDP512.h.

| #define TCTL1 DVUCP(0x0048) /* (M,L) 77,66,55,44 */ |

Definition at line 267 of file 9S12XDP512.h.

Referenced by initECTTimer().

| #define TCTL2 DVUCP(0x0049) /* (M,L) 33,22,11,00 */ |

Definition at line 268 of file 9S12XDP512.h.

Referenced by initECTTimer().

| #define TCTL1_ADDR AVUCP(0x0048) /* (M,L) 77,66,55,44 */ |

Definition at line 269 of file 9S12XDP512.h.

Referenced by initVariables().

| #define TCTL2_ADDR AVUCP(0x0049) /* (M,L) 33,22,11,00 */ |

Definition at line 270 of file 9S12XDP512.h.

Referenced by initVariables().

| #define DLYCT DVUCP(0x0069) /* Delay counter control register (minimum tooth width) */ |

Definition at line 274 of file 9S12XDP512.h.

| #define ICSYS DVUCP(0x006B) /* Input capture behaviour control register */ |

Definition at line 275 of file 9S12XDP512.h.

| #define ICOVW DVUCP(0x006A) /* Input capture overwrite allow */ |

Definition at line 276 of file 9S12XDP512.h.

| #define TCTL3 DVUCP(0x004A) /* (B,A) 77,66,55,44 */ |

Definition at line 284 of file 9S12XDP512.h.

Referenced by initECTTimer().

| #define TCTL4 DVUCP(0x004B) /* (B,A) 33,22,11,00 */ |

Definition at line 285 of file 9S12XDP512.h.

Referenced by decoderInitPreliminary(), initECTTimer(), perDecoderReset(), and SecondaryRPMISR().

| #define TC0H DVUSP(0x0078) /* 16 bit (0x0078 TC0H (hi), 0x0079 TC0H (lo)) */ |

Definition at line 288 of file 9S12XDP512.h.

| #define TC1H DVUSP(0x007A) /* 16 bit (0x007A TC1H (hi), 0x007B TC1H (lo)) */ |

Definition at line 289 of file 9S12XDP512.h.

| #define TC2H DVUSP(0x007C) /* 16 bit (0x007C TC2H (hi), 0x007D TC2H (lo)) */ |

Definition at line 290 of file 9S12XDP512.h.

| #define TC3H DVUSP(0x007E) /* 16 bit (0x007E TC3H (hi), 0x007F TC3H (lo)) */ |

Definition at line 291 of file 9S12XDP512.h.

| #define TC0 DVUSP(0x0050) /* 16 bit (0x0050 TC0 (hi), 0x0051 TC0 (lo)) */ |

Definition at line 294 of file 9S12XDP512.h.

Referenced by PrimaryRPMISR().

| #define TC1 DVUSP(0x0052) /* 16 bit (0x0052 TC1 (hi), 0x0053 TC1 (lo)) */ |

Definition at line 295 of file 9S12XDP512.h.

Referenced by SecondaryRPMISR().

| #define TC2 DVUSP(0x0054) /* 16 bit (0x0054 TC2 (hi), 0x0055 TC2 (lo)) */ |

Definition at line 296 of file 9S12XDP512.h.

| #define TC3 DVUSP(0x0056) /* 16 bit (0x0056 TC3 (hi), 0x0057 TC3 (lo)) */ |

Definition at line 297 of file 9S12XDP512.h.

| #define TC4 DVUSP(0x0058) /* 16 bit (0x0058 TC4 (hi), 0x0059 TC4 (lo)) */ |

Definition at line 298 of file 9S12XDP512.h.

| #define TC5 DVUSP(0x005A) /* 16 bit (0x005A TC5 (hi), 0x005B TC5 (lo)) */ |

Definition at line 299 of file 9S12XDP512.h.

| #define TC6 DVUSP(0x005C) /* 16 bit (0x005C TC6 (hi), 0x005D TC6 (lo)) */ |

Definition at line 300 of file 9S12XDP512.h.

| #define TC7 DVUSP(0x005E) /* 16 bit (0x005E TC7 (hi), 0x005F TC7 (lo)) */ |

Definition at line 301 of file 9S12XDP512.h.

| #define TC2_ADDR AVUSP(0x0054) /* 16 bit (0x0054 TC2 (hi), 0x0055 TC2 (lo)) */ |

Definition at line 303 of file 9S12XDP512.h.

Referenced by initVariables().

| #define TC3_ADDR AVUSP(0x0056) /* 16 bit (0x0056 TC3 (hi), 0x0057 TC3 (lo)) */ |

Definition at line 304 of file 9S12XDP512.h.

Referenced by initVariables().

| #define TC4_ADDR AVUSP(0x0058) /* 16 bit (0x0058 TC4 (hi), 0x0059 TC4 (lo)) */ |

Definition at line 305 of file 9S12XDP512.h.

Referenced by initVariables().

| #define TC5_ADDR AVUSP(0x005A) /* 16 bit (0x005A TC5 (hi), 0x005B TC5 (lo)) */ |

Definition at line 306 of file 9S12XDP512.h.

Referenced by initVariables().

| #define TC6_ADDR AVUSP(0x005C) /* 16 bit (0x005C TC6 (hi), 0x005D TC6 (lo)) */ |

Definition at line 307 of file 9S12XDP512.h.

Referenced by initVariables().

| #define TC7_ADDR AVUSP(0x005E) /* 16 bit (0x005E TC7 (hi), 0x005F TC7 (lo)) */ |

Definition at line 308 of file 9S12XDP512.h.

Referenced by initVariables().

| #define ICPAR DVUCP(0x0068) |

Definition at line 313 of file 9S12XDP512.h.

Referenced by decoderInitPreliminary().

| #define PACTL DVUCP(0x0060) |

Definition at line 317 of file 9S12XDP512.h.

| #define PAFLG DVUCP(0x0061) |

Definition at line 318 of file 9S12XDP512.h.

| #define PBCTL DVUCP(0x0070) |

Definition at line 319 of file 9S12XDP512.h.

| #define PBFLG DVUCP(0x0071) |

Definition at line 320 of file 9S12XDP512.h.

| #define PACNUS2 DVUSP(0x0062) /* 16 bit (0x0062 PACN3, 0x0063 PACN2) */ |

Definition at line 322 of file 9S12XDP512.h.

| #define PACNUS0 DVUSP(0x0064) /* 16 bit (0x0064 PACN1, 0x0065 PACN0) */ |

Definition at line 323 of file 9S12XDP512.h.

| #define PACN3 DVUCP(0x0062) /* high */ |

Definition at line 324 of file 9S12XDP512.h.

| #define PACN2 DVUCP(0x0063) /* low */ |

Definition at line 325 of file 9S12XDP512.h.

| #define PACN1 DVUCP(0x0064) /* high */ |

Definition at line 326 of file 9S12XDP512.h.

Referenced by decoderInitPreliminary(), and PrimaryRPMISR().

| #define PACN0 DVUCP(0x0065) /* low */ |

Definition at line 327 of file 9S12XDP512.h.

| #define PACHUS2 DVUSP(0x0072) /* 16 bit (0x0072 PACH3, 0x0073 PACH2) */ |

Definition at line 329 of file 9S12XDP512.h.

| #define PACHUS0 DVUSP(0x0074) /* 16 bit (0x0074 PACH1, 0x0075 PACH0) */ |

Definition at line 330 of file 9S12XDP512.h.

| #define PA3H DVUCP(0x0072) /* high */ |

Definition at line 331 of file 9S12XDP512.h.

| #define PA2H DVUCP(0x0073) /* low */ |

Definition at line 332 of file 9S12XDP512.h.

| #define PA1H DVUCP(0x0074) /* high */ |

Definition at line 333 of file 9S12XDP512.h.

| #define PA0H DVUCP(0x0075) /* low */ |

Definition at line 334 of file 9S12XDP512.h.

| #define MCCTL DVUCP(0x0066) /* Modulus control register */ |

Definition at line 338 of file 9S12XDP512.h.

| #define MCFLG DVUCP(0x0067) /* Modulus flag (high bit) and input edge indicators (low 4 bits) */ |

Definition at line 339 of file 9S12XDP512.h.

| #define MCCNT DVUSP(0x0076) /* 16 bit (0x0076 MCCNT (hi), 0x0077 MCCNT (lo)) */ |

Definition at line 340 of file 9S12XDP512.h.

| #define PTMCPSR DVUCP(0x006F) /* Precision prescaler for the modulus down counter */ |

Definition at line 341 of file 9S12XDP512.h.

| #define ATD1CTL0 DVUCP(0x0080) /* 0 - 3 define which ADC channel to wrap on when doing multiple channels */ |

Definition at line 346 of file 9S12XDP512.h.

Referenced by initADC().

| #define ATD1CTL1 DVUCP(0x0081) /* External trigger select when enabled in other control register */ |

Definition at line 347 of file 9S12XDP512.h.

| #define ATD1CTL2 DVUCP(0x0082) /* bit 7 turns the ADC block on. */ |

Definition at line 348 of file 9S12XDP512.h.

Referenced by initADC().

| #define ATD1CTL3 DVUCP(0x0083) /* bit 6 means conversion length is 8, bit 2 controls how the registers are used, bits 0 - 1 define freeze mode behaviour */ |

Definition at line 349 of file 9S12XDP512.h.

Referenced by initADC().

| #define ATD1CTL4 DVUCP(0x0084) /* bit 7 should be zero meaning 10bit ADC, bits 6,5 are the sample period, and 4,3,2,1,0 are the sample frequency clock scaler */ |

Definition at line 350 of file 9S12XDP512.h.

Referenced by initADC().

| #define ATD1CTL5 DVUCP(0x0085) /* bit 7 sets right justify, bit 5 sets scan mode, bit 4 sets multiplex mode */ |

Definition at line 351 of file 9S12XDP512.h.

Referenced by initADC().

| #define ATD1DIEN0 DVUCP(0x008C) /* Digital input enable - these pins are not bonded on the 112 pin package */ |

Definition at line 357 of file 9S12XDP512.h.

| #define ATD1DIEN1 DVUCP(0x008D) /* Digital input enable */ |

Definition at line 358 of file 9S12XDP512.h.

| #define ATD1_BASE 0x0090 |

Definition at line 362 of file 9S12XDP512.h.

Referenced by sampleLoopADC().

| #define ATD1DR0 DVUSP(ATD1_BASE + 0x0) /* 16 bit (0x0090 ATD1DR0H, 0x0091 ATD1DR0L) */ /* SpareADC (NC) */ |

Definition at line 363 of file 9S12XDP512.h.

Referenced by sampleEachADC().

| #define ATD1DR1 DVUSP(ATD1_BASE + 0x2) /* 16 bit (0x0092 ATD1DR1H, 0x0093 ATD1DR1L) */ /* SpareADC (NC) */ |

Definition at line 364 of file 9S12XDP512.h.

Referenced by sampleEachADC().

| #define ATD1DR2 DVUSP(ATD1_BASE + 0x4) /* 16 bit (0x0094 ATD1DR2H, 0x0095 ATD1DR2L) */ /* SpareADC (NC) */ |

Definition at line 365 of file 9S12XDP512.h.

Referenced by sampleEachADC().

| #define ATD1DR3 DVUSP(ATD1_BASE + 0x6) /* 16 bit (0x0096 ATD1DR3H, 0x0097 ATD1DR3L) */ /* SpareADC (NC) */ |

Definition at line 366 of file 9S12XDP512.h.

Referenced by sampleEachADC().

| #define ATD1DR4 DVUSP(ATD1_BASE + 0x8) /* 16 bit (0x0098 ATD1DR4H, 0x0099 ATD1DR4L) */ /* SpareADC (NC) */ |

Definition at line 367 of file 9S12XDP512.h.

Referenced by sampleEachADC().

| #define ATD1DR5 DVUSP(ATD1_BASE + 0xA) /* 16 bit (0x009A ATD1DR5H, 0x009B ATD1DR5L) */ /* SpareADC (NC) */ |

Definition at line 368 of file 9S12XDP512.h.

Referenced by sampleEachADC().

| #define ATD1DR6 DVUSP(ATD1_BASE + 0xC) /* 16 bit (0x009C ATD1DR6H, 0x009D ATD1DR6L) */ /* SpareADC (NC) */ |

Definition at line 369 of file 9S12XDP512.h.

Referenced by sampleEachADC().

| #define ATD1DR7 DVUSP(ATD1_BASE + 0xE) /* 16 bit (0x009E ATD1DR7H, 0x009F ATD1DR7L) */ /* SpareADC (NC) */ |

Definition at line 370 of file 9S12XDP512.h.

Referenced by sampleEachADC().

| #define SCI0_BASE 0x00C8 |

Definition at line 430 of file 9S12XDP512.h.

| #define SCI0BD DVUSP(SCI0_BASE + 0x0) /* #define SCI0BDH DVUCP(0x00C8), #define SCI0BDL DVUCP(0x00C9) (IR and baud control) */ |

Definition at line 432 of file 9S12XDP512.h.

Referenced by initSCIStuff().

Definition at line 433 of file 9S12XDP512.h.

Referenced by initSCIStuff().

Definition at line 435 of file 9S12XDP512.h.

Definition at line 436 of file 9S12XDP512.h.

Definition at line 437 of file 9S12XDP512.h.

Definition at line 439 of file 9S12XDP512.h.

Referenced by finaliseAndSend(), initSCIStuff(), resetReceiveState(), and SCI0ISR().

Definition at line 440 of file 9S12XDP512.h.

Referenced by resetReceiveState(), and SCI0ISR().

Definition at line 441 of file 9S12XDP512.h.

Definition at line 442 of file 9S12XDP512.h.

| #define SCI0DRL DVUCP(SCI0_BASE + 0x7) /* Data reg low (read and write for receive and send respectively)*/ |

Definition at line 443 of file 9S12XDP512.h.

Referenced by finaliseAndSend(), resetReceiveState(), and SCI0ISR().

| #define SPI0CR1 DVUCP(0x00D8) |

Definition at line 463 of file 9S12XDP512.h.

| #define SPI0CR2 DVUCP(0x00D9) |

Definition at line 464 of file 9S12XDP512.h.

| #define SPI0BR DVUCP(0x00DA) |

Definition at line 465 of file 9S12XDP512.h.

| #define SPI0SR DVUCP(0x00DB) |

Definition at line 466 of file 9S12XDP512.h.

| #define SPI0DR DVUCP(0x00DD) |

Definition at line 467 of file 9S12XDP512.h.

| #define FCLKDIV DVUCP(0x0100) /* Flash Clock Divider Register R/W */ |

Definition at line 495 of file 9S12XDP512.h.

Referenced by initFlash().

| #define FSEC DVUCP(0x0101) /* Flash Security Register R */ |

Definition at line 496 of file 9S12XDP512.h.

| #define FCNFG DVUCP(0x0103) /* Flash Configuration Register R/W */ |

Definition at line 497 of file 9S12XDP512.h.

| #define FPROT DVUCP(0x0104) /* Flash Protection Register R/W */ |

Definition at line 498 of file 9S12XDP512.h.

Referenced by initFlash().

| #define FSTAT DVUCP(0x0105) /* Flash Status Register R/W */ |

Definition at line 499 of file 9S12XDP512.h.

Referenced by eraseSector(), initFlash(), and writeWord().

| #define FCMD DVUCP(0x0106) /* Flash Command Register R/W */ |

Definition at line 500 of file 9S12XDP512.h.

Referenced by eraseSector(), and writeWord().

| #define FCTL DVUCP(0x0107) /* Flash Control Register R */ |

Definition at line 501 of file 9S12XDP512.h.

| #define FADDR DVUSP(0x0108) /* Flash Low Address Register R (0x0108 FADDRHI, 0x0109 FADDRLO) */ |

Definition at line 503 of file 9S12XDP512.h.

| #define FDATA DVUSP(0x010A) /* Flash High Data Register R (0x010A FDATAHI, 0x010B FDATALO) */ |

Definition at line 504 of file 9S12XDP512.h.

| #define IVBR DVUCP(0x0121) /* Interrupt vector table base location first byte (second is always 0x00) */ |

Definition at line 520 of file 9S12XDP512.h.

Referenced by initInterrupts().

| #define INT_XGPRIO DVUCP(0x0126) |

Definition at line 521 of file 9S12XDP512.h.

| #define INT_CFADDR DVUCP(0x0127) |

Definition at line 522 of file 9S12XDP512.h.

| #define INT_CFDATA0 DVUCP(0x0128) |

Definition at line 523 of file 9S12XDP512.h.

| #define INT_CFDATA_ARR AVUCP(0x0128) |

Definition at line 524 of file 9S12XDP512.h.

| #define INT_CFDATA1 DVUCP(0x0129) |

Definition at line 525 of file 9S12XDP512.h.

| #define INT_CFDATA2 DVUCP(0x012A) |

Definition at line 526 of file 9S12XDP512.h.

| #define INT_CFDATA3 DVUCP(0x012B) |

Definition at line 527 of file 9S12XDP512.h.

| #define INT_CFDATA4 DVUCP(0x012C) |

Definition at line 528 of file 9S12XDP512.h.

| #define INT_CFDATA5 DVUCP(0x012D) |

Definition at line 529 of file 9S12XDP512.h.

| #define INT_CFDATA6 DVUCP(0x012E) |

Definition at line 530 of file 9S12XDP512.h.

| #define INT_CFDATA7 DVUCP(0x012F) |

Definition at line 531 of file 9S12XDP512.h.

| #define CAN0CTL1 DVUCP(0x0141) |

Definition at line 564 of file 9S12XDP512.h.

| #define CAN1CTL1 DVUCP(0x0181) |

Definition at line 648 of file 9S12XDP512.h.

| #define CAN3CTL1 DVUCP(0x0201) |

Definition at line 720 of file 9S12XDP512.h.

| #define CAN4CTL1 DVUCP(0x0281) |

Definition at line 755 of file 9S12XDP512.h.

| #define ATD0CTL0 DVUCP(0x02C0) /* 0 - 2 define which ADC channel to wrap on when doing multiple channels */ |

Definition at line 790 of file 9S12XDP512.h.

| #define ATD0CTL1 DVUCP(0x02C1) /* External trigger select when enabled in other control register */ |

Definition at line 791 of file 9S12XDP512.h.

| #define ATD0CTL2 DVUCP(0x02C2) /* bit 7 turns the ADC block on. */ |

Definition at line 792 of file 9S12XDP512.h.

Referenced by initADC().

| #define ATD0CTL3 DVUCP(0x02C3) /* bit 6 means conversion length is 8, bit 2 controls how the registers are used, bits 0 - 1 define freeze mode behaviour */ |

Definition at line 793 of file 9S12XDP512.h.

Referenced by initADC().

| #define ATD0CTL4 DVUCP(0x02C4) /* bit 7 should be zero meaning 10bit ADC, bits 6,5 are the sample period, and 4,3,2,1,0 are the sample frequency clock scaler */ |

Definition at line 794 of file 9S12XDP512.h.

Referenced by initADC().

| #define ATD0CTL5 DVUCP(0x02C5) /* bit 7 sets right justify, bit 5 sets scan mode, bit 4 sets multiplex mode */ |

Definition at line 795 of file 9S12XDP512.h.

Referenced by initADC().

| #define ATD0DIEN DVUCP(0x02CD) /* Digital input enable */ |

Definition at line 798 of file 9S12XDP512.h.

| #define ATD0_BASE 0x02D0 /* Maybe use this with a loop to sample them in a compact way. */ |

Definition at line 800 of file 9S12XDP512.h.

Referenced by sampleLoopADC().

Definition at line 801 of file 9S12XDP512.h.

Referenced by adjustPWM(), and sampleEachADC().

Definition at line 802 of file 9S12XDP512.h.

Referenced by adjustPWM(), and sampleEachADC().

Definition at line 803 of file 9S12XDP512.h.

Referenced by adjustPWM(), and sampleEachADC().

Definition at line 804 of file 9S12XDP512.h.

Referenced by adjustPWM(), and sampleEachADC().

Definition at line 805 of file 9S12XDP512.h.

Referenced by adjustPWM(), and sampleEachADC().

Definition at line 806 of file 9S12XDP512.h.

Referenced by adjustPWM(), and sampleEachADC().

Definition at line 807 of file 9S12XDP512.h.

Referenced by adjustPWM(), and sampleEachADC().

Definition at line 808 of file 9S12XDP512.h.

Referenced by adjustPWM(), and sampleEachADC().

| #define VREGCTRL DVUCP(0x02F1) /* VReg Control Register */ |

Definition at line 812 of file 9S12XDP512.h.

Referenced by initInterrupts(), and LowVoltageISR().

| #define VREGAPICL DVUCP(0x02F2) /* Autonomous Periodical Interrupt Control Register */ |

Definition at line 813 of file 9S12XDP512.h.

| #define VREGAPITR DVUCP(0x02F3) /* Autonomous Periodical Interrupt Trimming Register */ |

Definition at line 814 of file 9S12XDP512.h.

| #define VREGAPIR DVUSP(0x02F4) /* Autonomous Periodical Interrupt Rate High and Low Registers (VREGAPIRH DVUCP(0x02F4), VREGAPIRL DVUCP(0x02F5)) */ |

Definition at line 815 of file 9S12XDP512.h.

| #define PWME DVUCP(0x0300) /* PWM enable register */ |

Definition at line 818 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMPOL DVUCP(0x0301) /* PWM polarity register */ |

Definition at line 819 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMCLK DVUCP(0x0302) /* PWM clock choice register */ |

Definition at line 820 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMPRCLK DVUCP(0x0303) /* PWM Clock prescalers (bits 0,1,2 and bits 4,5,6 control 4 pins each) */ |

Definition at line 821 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMCAE DVUCP(0x0304) /* PWM Center Align Enable Register */ |

Definition at line 822 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMCTL DVUCP(0x0305) /* PWM Concatenate, stop, wait, freeze register */ |

Definition at line 823 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMSCLA DVUCP(0x0308) /* PWM Scale A register */ |

Definition at line 824 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMSCLB DVUCP(0x0309) /* PWM Scale B register */ |

Definition at line 825 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMCNT0 DVUCP(0x030C) /* PWM 8 bit counter */ |

Definition at line 826 of file 9S12XDP512.h.

| #define PWMCNT1 DVUCP(0x030D) /* */ |

Definition at line 827 of file 9S12XDP512.h.

| #define PWMCNT2 DVUCP(0x030E) /* */ |

Definition at line 828 of file 9S12XDP512.h.

| #define PWMCNT3 DVUCP(0x030F) /* */ |

Definition at line 829 of file 9S12XDP512.h.

| #define PWMCNT4 DVUCP(0x0310) /* */ |

Definition at line 830 of file 9S12XDP512.h.

| #define PWMCNT5 DVUCP(0x0311) /* */ |

Definition at line 831 of file 9S12XDP512.h.

| #define PWMCNT6 DVUCP(0x0312) /* */ |

Definition at line 832 of file 9S12XDP512.h.

| #define PWMCNT7 DVUCP(0x0313) /* PWM 8 bit counter */ |

Definition at line 833 of file 9S12XDP512.h.

| #define PWMPER0 DVUCP(0x0314) /* PWM period value */ |

Definition at line 834 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMPER1 DVUCP(0x0315) /* */ |

Definition at line 835 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMPER2 DVUCP(0x0316) /* */ |

Definition at line 836 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMPER3 DVUCP(0x0317) /* */ |

Definition at line 837 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMPER4 DVUCP(0x0318) /* */ |

Definition at line 838 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMPER5 DVUCP(0x0319) /* */ |

Definition at line 839 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMPER6 DVUCP(0x031A) /* */ |

Definition at line 840 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMPER7 DVUCP(0x031B) /* PWM period value */ |

Definition at line 841 of file 9S12XDP512.h.

Referenced by initPWM().

| #define PWMDTY0 DVUCP(0x031C) /* PWM duty cycle value */ |

Definition at line 842 of file 9S12XDP512.h.

Referenced by adjustPWM(), and initPWM().

| #define PWMDTY1 DVUCP(0x031D) /* */ |

Definition at line 843 of file 9S12XDP512.h.

Referenced by adjustPWM(), and initPWM().

| #define PWMDTY2 DVUCP(0x031E) /* */ |

Definition at line 844 of file 9S12XDP512.h.

Referenced by adjustPWM(), and initPWM().

| #define PWMDTY3 DVUCP(0x031F) /* */ |

Definition at line 845 of file 9S12XDP512.h.

Referenced by adjustPWM(), and initPWM().

| #define PWMDTY4 DVUCP(0x0320) /* */ |

Definition at line 846 of file 9S12XDP512.h.

Referenced by adjustPWM(), and initPWM().

| #define PWMDTY5 DVUCP(0x0321) /* */ |

Definition at line 847 of file 9S12XDP512.h.

Referenced by adjustPWM(), and initPWM().

| #define PWMDTY6 DVUCP(0x0322) /* */ |

Definition at line 848 of file 9S12XDP512.h.

Referenced by adjustPWM(), and initPWM().

| #define PWMDTY7 DVUCP(0x0323) /* PWM duty cycle value */ |

Definition at line 849 of file 9S12XDP512.h.

Referenced by adjustPWM(), and initPWM().

| #define PWMSDN DVUCP(0x0324) /* PWM shutdown behaviour register */ |

Definition at line 850 of file 9S12XDP512.h.

| #define PITCFLMT DVUCP(0x0340) /* PIT Control and Force Load Micro Timer Register, high bit enables, low 2 bits force load micro timers */ |

Definition at line 854 of file 9S12XDP512.h.

| #define PITFLT DVUCP(0x0341) /* PIT Force Load Timer Register, low 4 bits force load timers */ |

Definition at line 855 of file 9S12XDP512.h.

| #define PITCE DVUCP(0x0342) /* PIT Channel Enable Register, low 4 bits let the channel count */ |

Definition at line 856 of file 9S12XDP512.h.

| #define PITMUX DVUCP(0x0343) /* PIT Multiplex Register, low 4 bits set which micro time base is used */ |

Definition at line 857 of file 9S12XDP512.h.

| #define PITINTE DVUCP(0x0344) /* PIT Interrupt Enable Register, low four bits control the ISRs */ |

Definition at line 858 of file 9S12XDP512.h.

Referenced by StagedOffISR(), and StagedOnISR().

| #define PITTF DVUCP(0x0345) /* PIT Time-Out Flag Register, low 4 bits set when each counter reaches 0 */ |

Definition at line 859 of file 9S12XDP512.h.

| #define PITMTLD0 DVUCP(0x0346) /* PIT Micro Timer Load Register 0, time to start counting from when reaching zero */ |

Definition at line 860 of file 9S12XDP512.h.

| #define PITMTLD1 DVUCP(0x0347) /* PIT Micro Timer Load Register 1, time to start counting from when reaching zero */ |

Definition at line 861 of file 9S12XDP512.h.

| #define PITLD0 DVUSP(0x0348) /* PIT Load Register 0, time to start counting from when reaching zero (0x0348 PITLD0 (hi), 0x0349 PITLD0 (lo)) */ |

Definition at line 862 of file 9S12XDP512.h.

| #define PITLD1 DVUSP(0x034C) /* PIT Load Register 1, time to start counting from when reaching zero (0x034C PITLD1 (hi), 0x034D PITLD1 (lo)) */ |

Definition at line 863 of file 9S12XDP512.h.

| #define PITLD2 DVUSP(0x0350) /* PIT Load Register 2, time to start counting from when reaching zero (0x0350 PITLD2 (hi), 0x0351 PITLD2 (lo)) */ |

Definition at line 864 of file 9S12XDP512.h.

| #define PITLD3 DVUSP(0x0354) /* PIT Load Register 3, time to start counting from when reaching zero (0x0354 PITLD3 (hi), 0x0355 PITLD3 (lo)) */ |

Definition at line 865 of file 9S12XDP512.h.

| #define PITCNT0 DVUSP(0x034A) /* PIT Count Register 0, current value of down counter (0x034A PITCNT0 (hi), 0x034B PITCNT0 (lo)) */ |

Definition at line 866 of file 9S12XDP512.h.

| #define PITCNT1 DVUSP(0x034E) /* PIT Count Register 1, current value of down counter (0x034E PITCNT1 (hi), 0x034F PITCNT1 (lo)) */ |

Definition at line 867 of file 9S12XDP512.h.

| #define PITCNT2 DVUSP(0x0352) /* PIT Count Register 2, current value of down counter (0x0352 PITCNT2 (hi), 0x0353 PITCNT2 (lo)) */ |

Definition at line 868 of file 9S12XDP512.h.

| #define PITCNT3 DVUSP(0x0356) /* PIT Count Register 3, current value of down counter (0x0356 PITCNT3 (hi), 0x0357 PITCNT3 (lo)) */ |

Definition at line 869 of file 9S12XDP512.h.

| #define XGMCTL DVUSP(0x0380) |

Definition at line 872 of file 9S12XDP512.h.

Referenced by XGATEErrorISR().

| #define XGMCTLHI DVUCP(0x0380) |

Definition at line 873 of file 9S12XDP512.h.

| #define XGMCTLLO DVUCP(0x0381) |

Definition at line 874 of file 9S12XDP512.h.

| #define XGCHID DVUCP(0x0382) |

Definition at line 875 of file 9S12XDP512.h.

| #define XGVBR DVUSP(0x0386) /* This is all that is used on the xdp512! 16 bit (0x0386 DVUCP (hi), 0x0387 DVUCP (lo)) */ |

Definition at line 878 of file 9S12XDP512.h.

| #define XGIF_0 DVUCP(0x0388) |

Definition at line 879 of file 9S12XDP512.h.

| #define XGIF_1 DVUCP(0x0389) |

Definition at line 880 of file 9S12XDP512.h.

| #define XGIF_2 DVUCP(0x038A) |

Definition at line 881 of file 9S12XDP512.h.

| #define XGIF_3 DVUCP(0x038B) /* WRONG value 0x023B stated in the manual as being both xgate and can3!!!!! should be 0x038B i believe!!!!! */ |

Definition at line 882 of file 9S12XDP512.h.

| #define XGIF_4 DVUCP(0x038C) /* WRONG value 0x023C stated in the manual as being both xgate and can3!!!!! should be 0x038C i believe!!!!! */ |

Definition at line 883 of file 9S12XDP512.h.

| #define XGIF_5 DVUCP(0x038D) |

Definition at line 884 of file 9S12XDP512.h.

| #define XGIF_6 DVUCP(0x038E) |

Definition at line 885 of file 9S12XDP512.h.

| #define XGIF_7 DVUCP(0x038F) |

Definition at line 886 of file 9S12XDP512.h.

| #define XGIF_8 DVUCP(0x0390) |

Definition at line 887 of file 9S12XDP512.h.

| #define XGIF_9 DVUCP(0x0391) |

Definition at line 888 of file 9S12XDP512.h.

| #define XGIF_A DVUCP(0x0392) |

Definition at line 889 of file 9S12XDP512.h.

| #define XGIF_B DVUCP(0x0393) |

Definition at line 890 of file 9S12XDP512.h.

| #define XGIF_C DVUCP(0x0394) |

Definition at line 891 of file 9S12XDP512.h.

| #define XGIF_D DVUCP(0x0395) |

Definition at line 892 of file 9S12XDP512.h.

| #define XGIF_E DVUCP(0x0396) |

Definition at line 893 of file 9S12XDP512.h.

| #define XGIF_F DVUCP(0x0397) |

Definition at line 894 of file 9S12XDP512.h.

| #define XGSWT DVUSP(0x0398) |

Definition at line 895 of file 9S12XDP512.h.

| #define XGSEM DVUSP(0x039A) |

Definition at line 897 of file 9S12XDP512.h.

| #define XGCCR DVUCP(0x039D) |

Definition at line 899 of file 9S12XDP512.h.

| #define XGPC DVUSP(0x039E) |

Definition at line 900 of file 9S12XDP512.h.

| #define XGR1 DVUSP(0x03A2) |

Definition at line 902 of file 9S12XDP512.h.

| #define XGR2 DVUSP(0x03A4) |

Definition at line 904 of file 9S12XDP512.h.

| #define XGR3 DVUSP(0x03A6) |

Definition at line 906 of file 9S12XDP512.h.

| #define XGR4 DVUSP(0x03A8) |

Definition at line 908 of file 9S12XDP512.h.

| #define XGR5 DVUSP(0x03AA) |

Definition at line 910 of file 9S12XDP512.h.

| #define XGR6 DVUSP(0x03AC) |

Definition at line 912 of file 9S12XDP512.h.

| #define XGR7 DVUSP(0x03AE) |

Definition at line 914 of file 9S12XDP512.h.

1.8.1.2

1.8.1.2